- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- U-Boot Does not work with i.MX6Q and MMPF0100 default F0 ROM.

U-Boot Does not work with i.MX6Q and MMPF0100 default F0 ROM.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

U-Boot Does not work with i.MX6Q and MMPF0100 default F0 ROM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear community.

Our customer has question below.

Customer evaluating own board using CPU: i.MX6Quad, PMIC: MMPF0100F0ANESR2.

But when power supply problems occur that boot from the boot device (eMMC used) specified by the BOOT_CFG pin of the CPU .

By the way, it will start up by manually controlling the reset signal POR_B (H → L → H)is no problem, we believe there is no mistake in the setting of the BOOT_CFG pin itself.

For the cause investigation, the power supply start sequence of SABRE - SDB and customer board was compared.

As a problem, on the customer board, it turned out that POR_B output by PMIC was controlled to H (reset release) before VDDARM_CAP was output.

※ In the SABRE-SDB, this order is reverse.

This is contrary to the following description of the reference manual IMX6DQRM, P.5084, so I think that a problem has occurred.

60.5.1 External POR using SRC_POR_B

If the external SRC_POR_B signal is used to control the processor POR, SRC_POR_B must remain low (asserted) until the VDD_ARM_CAP and VDD_SOC_CAP supplies are stable.

<question>

1, Does SABRE - SDB use the default "F 0 "OTP setting?

Customer used F0 OTP settings.

2,Is SABRE-SDB doing OTP rewriting / customization from the default "F0"?

3,On the SABRE-SDB, when "F0" OTP is being rewritten, which address

What kind of values are rewriting?

4,When OTP is not rewritten, what will be assumed as the reason for the difference in the timing of the power supply

startup sequence between the SABRE-SDB and customer board?

5,I tried AN4546 (MMPF0100 OTP Programming Instructions) method to change the PMIC timing, but I could read

registers other than OTP, but I can not access the OTP region register.

Address 0x80 Is OTP FUSE READ EN required to write 0x01 before reading OTP?

6,When the output voltage of MCIMX 6Q-SDB was measured with an oscilloscope here

In the default sequence of PMIC F 0

9th VGEN 1

10th VGEN 2

11th VGEN 3

12 th VGEN 5,

In actual measurement

VGEN 1 and VGEN 2, VGEN 3 and VGEN 5 are running at the same timing, respectively.

Is it a custom OTP rather than the default sequence of F0?

Thank you,

Best Regards.

T.Takahashi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Takahashi,

1, Does SABRE - SDB use the default "F 0 "OTP setting?

Customer used F0 OTP settings.

Yes,it does. F0 is correct.

2,Is SABRE-SDB doing OTP rewriting / customization from the default "F0"?

No, it is not. if OTP was done, it can't be done again.

3,On the SABRE-SDB, when "F0" OTP is being rewritten, which address

What kind of values are rewriting?

About F0, We have a script provided by Power team, you should download it from offical website.

But MMPF0100F0ANES is F0 configuration, customer can't do OTP again.

4,When OTP is not rewritten, what will be assumed as the reason for the difference in the timing of the power supply

startup sequence between the SABRE-SDB and customer board?

you can check follwing items when power up:

(1) Is PWRON pin HIGH?

(2) Is VDDOTP pin is LOW?( the status is "start up from OTP)"?

(3) Does VSNVS output 3.0V?

(4) Is POR_B pin of CPU HIGH?

5,I tried AN4546 (MMPF0100 OTP Programming Instructions) method to change the PMIC timing, but I could read

registers other than OTP, but I can not access the OTP region register.

Address 0x80 Is OTP FUSE READ EN required to write 0x01 before reading OTP?

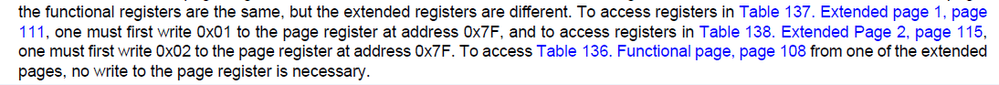

0x7F register should be 0x01 / 0x02. then you can read OTP registers.

6,When the output voltage of MCIMX 6Q-SDB was measured with an oscilloscope here

In the default sequence of PMIC F 0

9th VGEN 1

10th VGEN 2

11th VGEN 3

12 th VGEN 5,

these VGENs can't affect CPU booting.

>>Is it a custom OTP rather than the default sequence of F0?

It is the default sequence of F0.

Best Regards,

Weidong