- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- On the AUD3 I.MX6DQRM output clock 44.1 frequency offset problem?

On the AUD3 I.MX6DQRM output clock 44.1 frequency offset problem?

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

On the AUD3 I.MX6DQRM output clock 44.1 frequency offset problem?

11-28-2016

07:29 PM

688 Views

shaoxuemei

Contributor I

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are now using I.MX6DQRM crystal for 24Mhz, we use the crystal frequency division to aud3, but we found that the frequency of aud3 is not what we want 44.1KHz, but 44.3khz, to solve this problem we find the relevant documents, the formula is:

PLL output frequency = Fref * (DIV_SELECT + NUM/DENOM)

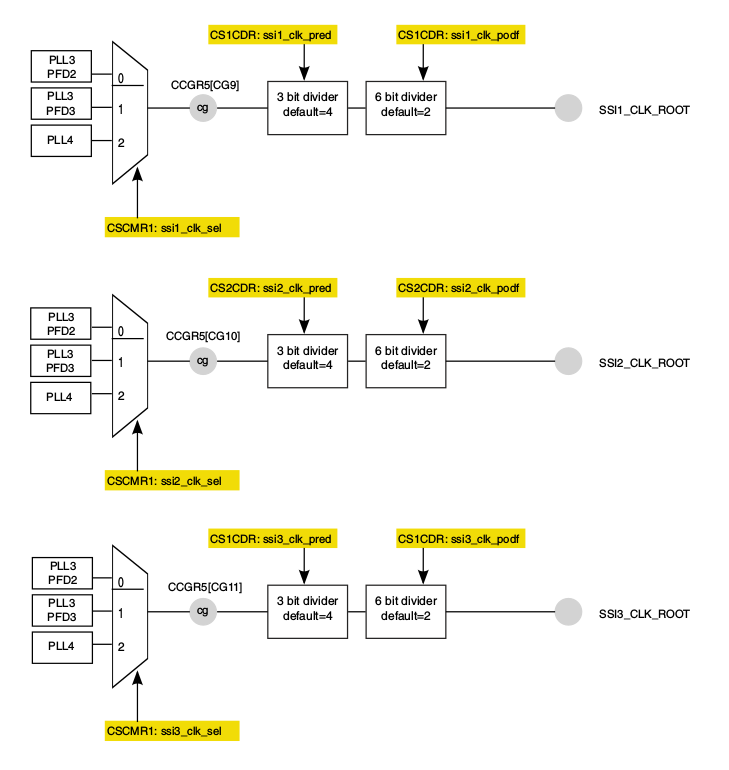

Also view the related clock generation Serial (cont):

Our kernel inside is the definition of the AUD3 output frequency dependent parameters(Annex for the complete documentation):

/* Let's initially set up CLKO with OSC24M, since this configuration is widely used by imx6q board designs to clock audio codec.*/

imx_clk_set_parent(clk[IMX6QDL_PLL4_BYPASS_SRC],clk[IMX6QDL_CLK_OSC]);

imx_clk_set_rate(clk[IMX6QDL_CLK_PLL4], 1179648000);

imx_clk_set_rate(clk[IMX6QDL_CLK_PLL4_AUDIO_DIV], 589824000); //johnli add 24576000X8=541900800

imx_clk_set_parent(clk[IMX6QDL_CLK_SSI2_SEL], clk[IMX6QDL_CLK_PLL4_AUDIO_DIV]);//johnli add

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI2_PRED], 147456000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI2_PODF], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI2], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_parent(clk[IMX6QDL_CLK_SSI3_SEL], clk[IMX6QDL_CLK_PLL4_AUDIO_DIV]);//johnli add

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI3_PRED], 147456000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI3_PODF], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI3], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_parent(clk[IMX6QDL_CLK_SSI1_SEL], clk[IMX6QDL_CLK_PLL4_AUDIO_DIV]);//johnli add

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI1_PRED], 147456000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI1_PODF], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI1], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_parent(clk[IMX6QDL_CLK_CKO2_SEL], clk[IMX6QDL_CLK_SSI2]);//johnli changed

/* Let's initially set up CLKO with OSC24M, since this configuration is widely used by imx6q board designs to clock audio codec.*/

//johnli changed clko from ssi2

// imx_clk_set_rate(clk[IMX6QDL_PLL4_BYPASS_SRC], 180633600); //johnli add 196608000X4=786432000imx_clk_set_parent(clk[IMX6QDL_PLL4_BYPASS_SRC],clk[IMX6QDL_CLK_OSC]);

imx_clk_set_rate(clk[IMX6QDL_CLK_PLL4], 1179648000);

imx_clk_set_rate(clk[IMX6QDL_CLK_PLL4_AUDIO_DIV], 589824000); //johnli add 24576000X8=541900800

imx_clk_set_parent(clk[IMX6QDL_CLK_SSI2_SEL], clk[IMX6QDL_CLK_PLL4_AUDIO_DIV]);//johnli add

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI2_PRED], 147456000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI2_PODF], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI2], 24576000); //johnli add 48000X512=24576000 22579200

//add for ssi3

imx_clk_set_parent(clk[IMX6QDL_CLK_SSI3_SEL], clk[IMX6QDL_CLK_PLL4_AUDIO_DIV]);//johnli add

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI3_PRED], 147456000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI3_PODF], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI3], 24576000); //johnli add 48000X512=24576000 22579200

//add for ssi1

imx_clk_set_parent(clk[IMX6QDL_CLK_SSI1_SEL], clk[IMX6QDL_CLK_PLL4_AUDIO_DIV]);//johnli add

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI1_PRED], 147456000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI1_PODF], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_rate(clk[IMX6QDL_CLK_SSI1], 24576000); //johnli add 48000X512=24576000 22579200

imx_clk_set_parent(clk[IMX6QDL_CLK_CKO2_SEL], clk[IMX6QDL_CLK_SSI2]);//johnli changed

imx_clk_set_parent(clk[IMX6QDL_CLK_CKO], clk[IMX6QDL_CLK_CKO2]);

Now we need to calculate or change the parameters to achieve the AUD3 output frequency of 44.1?

Best regards,

Xuemei Shao

Original Attachment has been moved to: clk-imx6q.c.zip

0 Replies