- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- P-Series

- :

- TDM UMCC synchronization in transparent mode

TDM UMCC synchronization in transparent mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TDM UMCC synchronization in transparent mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We are currently writing a driver to operate a T1040 QuiccEngine TDM link with UMCC feature.

This link is supposed to work in transparent mode, and we do not need to use any synchronization pattern.

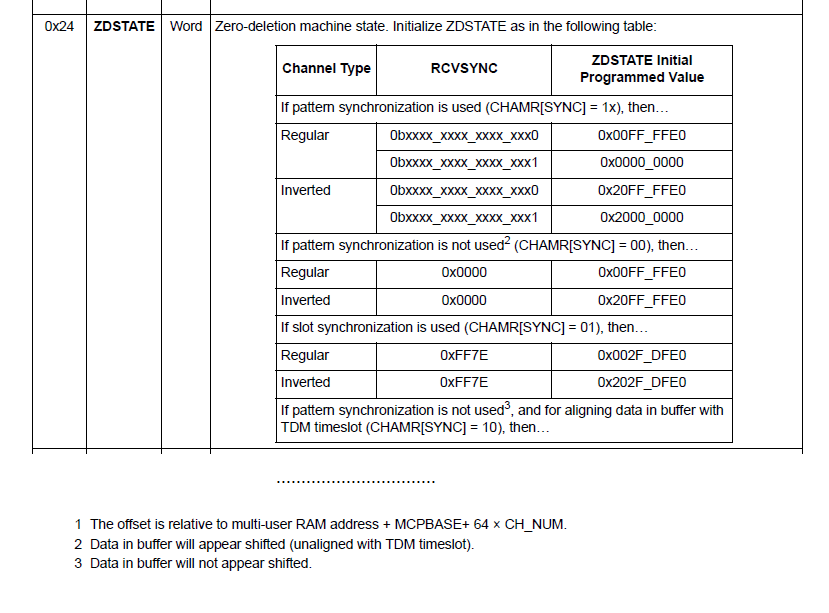

We have first tried to deactivate the synchronization by setting CHAMR[SYNC] = 0 but the received data are shifted. This is specified in MCC 23.2.2.2 chapter of the QEIWRM. Even if related to the MCC, I suppose this restriction is also applicable to the UMCC.

We have also tried to configure an 8-bit synchronization pattern which works fine for 8-bit time slots, but data in 16-bit time slots is always shifted, even with a 16-bit pattern.

The picture above seems to show a configuration where no pattern is used and data is not shifted (note 3) but the RCVSYNC and ZDSTATE informations are missing...

Could someone please provide us with the missing configuration?

Many thanks,

Sébastien

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your feedback.

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Pavel,

Thank you for this example.

The issue is solved and the answer was in a previous release of the QEWRM (rev. 4). Unfortunately it was removed from the present release!

It seems that "RCVSYNC = 0xFF7E" is to be set so as to keep data aligned without using the synchronization mechanism.

It now works perfectly for us.

Regards,

Sébastien

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Look at attached file.

It is simple program example for the MPC8560 MCC in transparent mode. Compare this example and your settings.

Have a great day,

Pavel Chubakov

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------