- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Unused SNVS_TAMPER pins of IMX6UL

Unused SNVS_TAMPER pins of IMX6UL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We are designing a PCB with IMX6UL processor(Part No: MCIMX6G2DVM05AA).

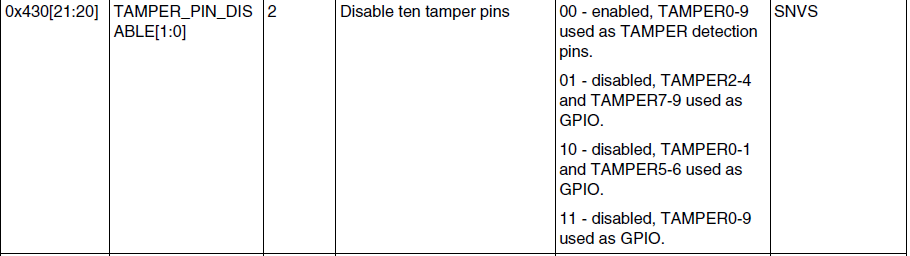

According to TAMPER_PIN_DISABLE[1:0] ,the pins can either be enabled for tamper detection or used as GPIO.

(Please find the following configuration as on Pg214 of IMX6UL reference manual.)

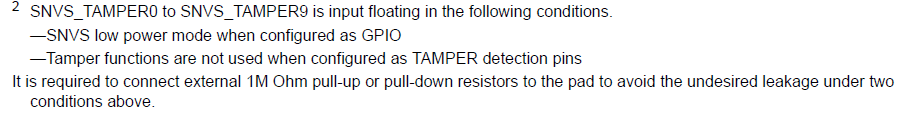

Also page 131 of IMX6UL datasheet specifies that 1M to be added in the following conditions.

1.When the tamper pins are configured as GPIOs

2.When the pins are enabled for tamper detection.

Q1: Does the above reference means that 1M resistor be added to the SNVS_TAMPER pins, on all the above cases.

Also can you please clarify the handling of SNVS_TAMPER pins in the design, for the following conditions.

Q2.The SNVS tamper pins are not used either as GPIOs or for tamper detection function.

Does all the 10 pins (SNVS_TAMPER[0:9]) require 1M resistor to GND(or pulled up to SNVS).

Can the pins be left floating ?

Q3.Only certain tamper pins are configured as GPIOs(as specified by the bits in TAMPER_PIN_DISABLE[1:0]) in SNVS_TAMPER[0:9].Can 1M pull down/pull up resistors be added only for them.

Thanks in anticipation.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The case, when the SNVS_TAMPER pins are configured as tampers and tamper functions

are used, there is no need for the 1M resistor : external scheme should provide expected

voltage level for tamper event.

If power consumption is not the problem for Your system it is possible to configure

the pins as GPIO input and use internal resistors for pulling or keepers.

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct

Answer button. Thank you!

------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The case, when the SNVS_TAMPER pins are configured as tampers and tamper functions

are used, there is no need for the 1M resistor : external scheme should provide expected

voltage level for tamper event.

If power consumption is not the problem for Your system it is possible to configure

the pins as GPIO input and use internal resistors for pulling or keepers.

Have a great day,

Yuri

------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct

Answer button. Thank you!

------------------------------------------------------------------------------