- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- FTM counter reset / start couting on external trigger event?

FTM counter reset / start couting on external trigger event?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello all,

currently I'm trying to port an application from a MC56F847 controller to a Kinetis V4x controller. Therefore I need and an FTM counter to start counting based on an the beginning of an PWM cycle / signal. After two configureable delays I need to enable two outputs (independently).

So here is my concept so far:

- PWM generation: PWMA_0A -> PWMA0_TRG0

- Connection between PWM & FTM component: PWMA_A0_TRG0 -> over xbar -> FTM0_TRIG2

- Two channels as output compar mode: FTM0_CH0 & FTM0_CH1

I use the following code o initializ the timer component:

ftmConfig.extTriggers =kFTM_Chnl0Trigger;

ftmConfig.chnlInitState =0;

ftmConfig.pwmSyncMode =kFTM_HardwareTrigger_2;

if (FTM_Init(FTM0, &ftmConfig) != kStatus_Success)

{

return false;

}

FTM_SetupOutputCompare(FTM0, kFTM_Chnl_0, kFTM_SetOnMatch, 1000);

FTM0->SYNC |= (1<<2); // reinit

FTM0->CNTIN =0U;

FTM0->MOD =0xFFFFU;

And here the problem begins. If I now enable the timer via FTM_StartTimer(...) it starts counting and the channel 0 output will be set after a while. Is it possible start the counting when the signal TRIG2 occurs? The other problem is, that the counter currently just overflows and starts counting from zero again - but it should stop counting and reset the outputs to their initial values - is that possible?

Best Regards,

Florian

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello XiangJun,

thanks again for your fast response. After changing the trigger signal as explained the synchronization wasn't working (xbarin-xbarout34 and the direct soultion (pwma0_trig0 - xbarout34)). After reading the reference manual again and again I have found the comment "only the enhanced PWM synchronization must be used" - so my gues is that the legacy PWM mode shouldn't be used on this device right? I have changed the corresponding bit in the SYSCONF register and now its working. I have attached the working code - if someone else will have the same issue in the future....

Best Regards,

Florian

<CODE>

CLOCK_EnableClock(kCLOCK_PortC);

CLOCK_EnableClock(kCLOCK_Ftm0);

PORT_SetPinMux(PORTC, 1u, kPORT_MuxAlt4); // FTM0_CH0 on PTC1

PORT_SetPinMux(PORTC, 2u, kPORT_MuxAlt4); // FTM0_CH1 on PTC2

XBARA_SetSignalsConnection(XBARA, kXBARA_InputPwm0Trg0, kXBARA_OutputFtm0Trig2); // connect kXBARA_InputPwm0Trg0 to kXBARA_OutputFtm0Trig2

// configure hardware trigger

SIM->SOPT4 |= (SIM_SOPT4_FTM0TRG2SRC_MASK);

FTM0->SYNC |= 0x40; // enable hw trigger 2

FTM0->SYNCONF |= 0x30081;

// configure PWM on FTM0_CH0/1 (PTC1/2)

FTM0->CONF=0xC0; //set up BDM in 11

FTM0->FMS=0x00; //clear the WPEN so that WPDIS is set in FTM0_MODE reg

FTM0->MODE|=0x05; //enable write the FTM CnV register

FTM0->MOD=2000;

FTM0->CONTROLS[0].CnSC=0x28; //High_Low_High for center-alignment

FTM0->CONTROLS[1].CnSC=0x28; //High_Low_High for center-alignment

FTM0->COMBINE|=0x20; //enable update the FTM_C0V/FTM0_C1V register

FTM0->COMBINE|=0x02; //complementary mode for CH0&CH1 of FTM0

FTM0->COMBINE|=0x10; // dead timer insertion enabled in complementary mode for //CH0&CH1 of

FTM0->DEADTIME=0x00; //dead time is 0 system clock cycles

FTM0->CONTROLS[1].CnV=500;

FTM0->CONTROLS[0].CnV=500;

FTM0->CNTIN=0x00;

FTM0->SC=0x08; // system clock driving, dividing by 1

</CODE>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i think counter will count till MOD value. In this case MOD is 0xFFFF so it will count till max value. try changing MOD value to your desired value

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello sumit,

thanks for your response but the overflow itself isn't the problem - the hardware trigger doesn't work as expected which should reset the counter long time before the overlfow happens.

Best Regards,

Florian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Florian,

I think your solution is okay.

You have the PWMA_0A triggering signals(XBARA_IN20 or PWMA0_TRG0) route to FTM0_TRIG2(XBARA_OUT34) via crossbar, and use the FTM0_TRIG2 to synchronize FTM0 counter. You can set the FTM0 MOD register as the maximum value 0xFFFF, when the FTM0_TRIG2 signal arrives, the FTM counter FTM0_CNT register is initialized by the FTM0_CNTIN register, the FTM0_CNT will begin to count from the FTM0_CNTIN value. The FTM_StartTimer(...) function only sets the CLKS bits in FTM0_SC register so that the FTM0_CNT begins to count. As I said the FTM0_CNT will be initialized with FTM0_CNTIN value when the rising edge of FTM0_TRIG2 comes.

I suggest you refer to an5142, which has the code for hardware triggering.

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello XiangJun,

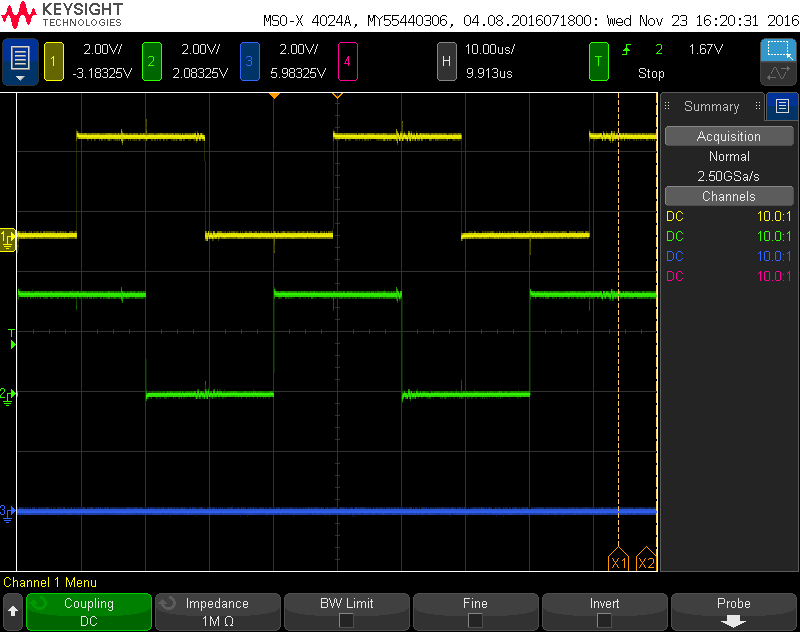

thanks for your fast response. I have tried the exmaple in chapter 3.11.4 (Updating the FTM register with hardware control) which was the base for my previous tests. I have used the code from the application note with only one change - I have to use FTM0_FLT1 instead of FTM0_FLT0. I can't get the example running...I have also attached the a screenshot of the signals. The yellow one show the input signal of FTM0_FLT1 (GC0) and the green one show the signal of PTC1 - you can see that the rising edge of the yellow signal is ignored by the timer component. Any suggestions / ideas?

Best Regards,

Florian

<CODE>

CLOCK_EnableClock(kCLOCK_PortC);

CLOCK_EnableClock(kCLOCK_Ftm0);

PORT_SetPinMux(PORTC, 0u, kPORT_MuxAlt6); // FTM0_FLT1 (alt6) on PTC0

PORT_SetPinMux(PORTC, 1u, kPORT_MuxAlt4); // FTM0_CH0 on PTC1

PORT_SetPinMux(PORTC, 2u, kPORT_MuxAlt4); // FTM0_CH1 on PTC2

// configure hardware trigger

SIM->SOPT4 &=~(SIM_SOPT4_FTM0FLT1_MASK);

FTM0->SYNC |= 0x40; // enable hw trigger 2

FTM0->SYNCONF |= 0x30001;

// configure PWM on FTM0_CH0/1 (PTC1/2)

FTM0->CONF=0xC0; //set up BDM in 11

FTM0->FMS=0x00; //clear the WPEN so that WPDIS is set in FTM0_MODE reg

FTM0->MODE|=0x05; //enable write the FTM CnV register

FTM0->MOD=1000;

FTM0->CONTROLS[0].CnSC=0x28; //High_Low_High for center-alignment

FTM0->CONTROLS[1].CnSC=0x28; //High_Low_High for center-alignment

FTM0->COMBINE|=0x20; //enable update the FTM_C0V/FTM0_C1V register

FTM0->COMBINE|=0x02; //complementary mode for CH0&CH1 of FTM0

FTM0->COMBINE|=0x10; // dead timer insertion enabled in complementary mode for //CH0&CH1 of

FTM0->DEADTIME=0x00; //dead time is 0 system clock cycles

FTM0->CONTROLS[1].CnV=500;

FTM0->CONTROLS[0].CnV=500;

FTM0->CNTIN=0x00;

FTM0->SC=0x28; //PWM center_alignment, system clock driving, dividing by 1

</CODE>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Florian,

I suppose that you can NOT use FTM0_FLT1(PTC0) as hardware triggering signal. Pls refer to sectin 39.1.6 FTM Hardware Triggers in the reference manual of KV4x, only XBARA_OUT34 can be used as FTM0 hardware triggering source2. If you want to use external signal as FTM0 hardware triggering source2, you can connect the signal to any XB_INx pin and route the signal to XBARA_OUT34.

for example, you can connect the external triggering signal to PTC5/XBAR0_IN2

CLOCK_EnableClock(kCLOCK_PortC);

PORT_SetPinMux(PORTC, 5u, kPORT_MuxAlt4); //PTC5 as XBAR0_IN2/ALT4

XBARA_SEL17&=~(0x3F);

XBARA_SEL17|=0x02; //route the XBAR0_IN2 to XBARA_OUT34.

If you use the PWMA_0A triggering signal

XBARA_SEL17&=~(0x3F);

XBARA_SEL17|=20; //route the PWMA0_TRG0 to XBARA_OUT34.

Hope it can help you

BR

Xiangjun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello XiangJun,

thanks again for your fast response. After changing the trigger signal as explained the synchronization wasn't working (xbarin-xbarout34 and the direct soultion (pwma0_trig0 - xbarout34)). After reading the reference manual again and again I have found the comment "only the enhanced PWM synchronization must be used" - so my gues is that the legacy PWM mode shouldn't be used on this device right? I have changed the corresponding bit in the SYSCONF register and now its working. I have attached the working code - if someone else will have the same issue in the future....

Best Regards,

Florian

<CODE>

CLOCK_EnableClock(kCLOCK_PortC);

CLOCK_EnableClock(kCLOCK_Ftm0);

PORT_SetPinMux(PORTC, 1u, kPORT_MuxAlt4); // FTM0_CH0 on PTC1

PORT_SetPinMux(PORTC, 2u, kPORT_MuxAlt4); // FTM0_CH1 on PTC2

XBARA_SetSignalsConnection(XBARA, kXBARA_InputPwm0Trg0, kXBARA_OutputFtm0Trig2); // connect kXBARA_InputPwm0Trg0 to kXBARA_OutputFtm0Trig2

// configure hardware trigger

SIM->SOPT4 |= (SIM_SOPT4_FTM0TRG2SRC_MASK);

FTM0->SYNC |= 0x40; // enable hw trigger 2

FTM0->SYNCONF |= 0x30081;

// configure PWM on FTM0_CH0/1 (PTC1/2)

FTM0->CONF=0xC0; //set up BDM in 11

FTM0->FMS=0x00; //clear the WPEN so that WPDIS is set in FTM0_MODE reg

FTM0->MODE|=0x05; //enable write the FTM CnV register

FTM0->MOD=2000;

FTM0->CONTROLS[0].CnSC=0x28; //High_Low_High for center-alignment

FTM0->CONTROLS[1].CnSC=0x28; //High_Low_High for center-alignment

FTM0->COMBINE|=0x20; //enable update the FTM_C0V/FTM0_C1V register

FTM0->COMBINE|=0x02; //complementary mode for CH0&CH1 of FTM0

FTM0->COMBINE|=0x10; // dead timer insertion enabled in complementary mode for //CH0&CH1 of

FTM0->DEADTIME=0x00; //dead time is 0 system clock cycles

FTM0->CONTROLS[1].CnV=500;

FTM0->CONTROLS[0].CnV=500;

FTM0->CNTIN=0x00;

FTM0->SC=0x08; // system clock driving, dividing by 1

</CODE>