- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- question about flexpwm of MPC5744P

question about flexpwm of MPC5744P

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

question about flexpwm of MPC5744P

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

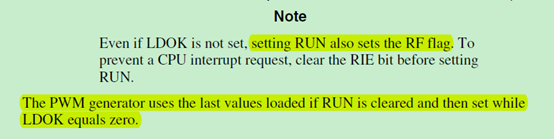

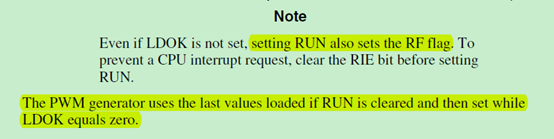

Q1: when I write Run=0 and then write Run=1, will flexPWM generate Local Reload Signal?

Q2: SUBn_CTRL1[PRSC], SUBn_INIT and SUBn_VALx have buffers. I want to ask when I configure these registers the first time after reset, where did I write to? the outer buffers or the inner?

Q3: (fellow Q2) if the answer is the outer buffers, what is happening when I set Run=1?

As I think it will first generate local reload signal, secondly reload the buffers to the inner, at last run as I have configured. Is that correct? If no what is the right process?

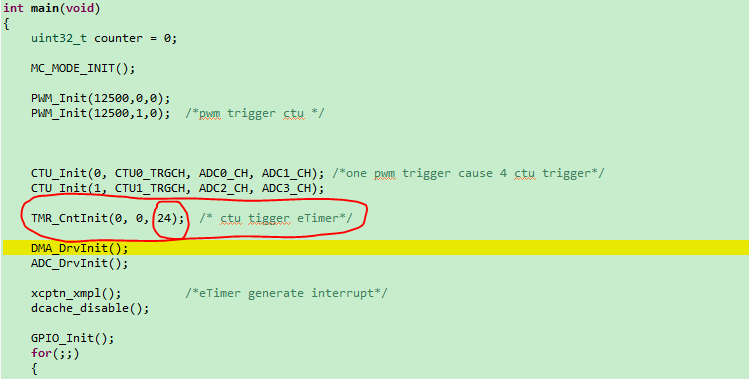

Q4: in my program I use flexpwm0 pwmx0 trigger ctu0, flexpwm1 pwmx0 trigger ctu1, and ctu0&ctu1 trigger ADC0-3, so I configure flexpwm1 use EXT_SYNC to Initialize itself. The code is as follows:

FlexPWM1.SUB[0].CTRL2.B.INIT_SEL = 3; /* 11 = EXT_SYNC causes initialization */

where the ext_sync signal to flexpwm1 is the master reload signal of flexpwm0.

A strange thing I found is that at the first cycle of flexpwm1, flexpwm1 seems cann’t trigger ctu1. After the first cycle, the flexpwm1 trigger ctu1 well. i want know why?

PS: when I configure flexpwm1 INIT_SEL=0 (local sync cause initilation), it will be ok.

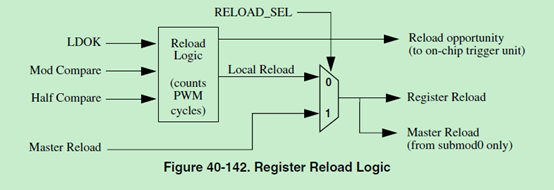

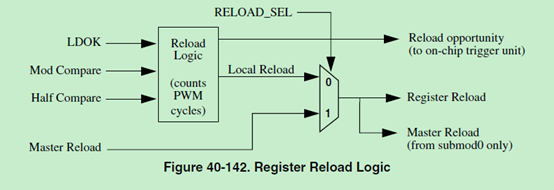

Q5: Another thing I found is that under this condition( flexpwm1 INIT_SEL=3), it seems that when I set flexpwm0 Run=0 and then set flexpwm0 Run=1, it will reset flexpwm1 counter register((FlexPWM_SUBn_CNT) , does that mean a master reload signal has generated?

Thank you very much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Problem solved!(By Doctor Gong)

Give a record here:

原因是FlexPWM0产生的reload信号(用于同步FlexPWM1)在一个采样循环内周期不一致,即同步运行后的第一个cycle中reload周期偏小。这是因为在FlexPWM0从RUN=0倒RUN=1的过程中,COUNTER没有初始化。

改进如下:

在PWM初始化函数void PWM_Init(uint16_t PWMFre, uint8_t nbPWM, uint8_t nCH)中,增加如下代码即可:

p_PWM->SUB[nCH].CTRL2.B.FRCEN = 1;

p_PWM->SUB[nCH].CTRL2.B.FORCE_SEL = 2;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

A1) upon reset yes. Otherwise it depends on the counter value

A2) to the set of outer buffer

A3) you are correct

A4) try to measure PWMx signal with a scope, and see what happens on it in first period.

Within CTU you can select rising or falling edge of PWMX for MSR trigger. Did you test both options?

A5) yes, Master reload was generated.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

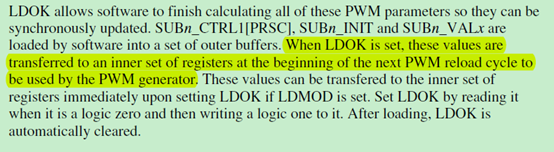

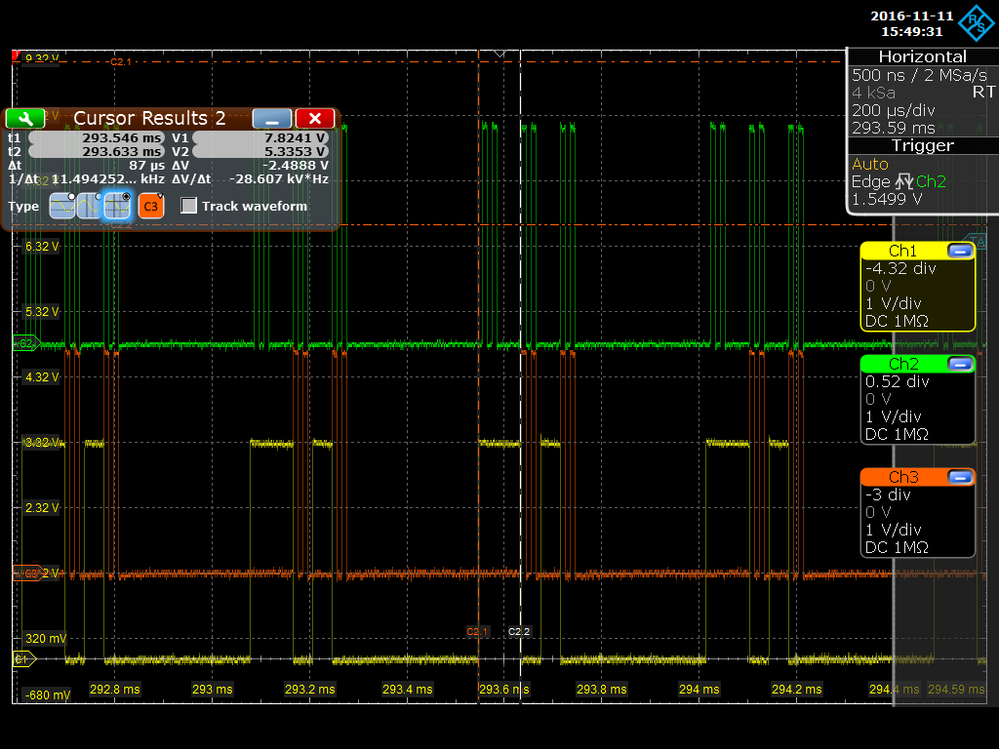

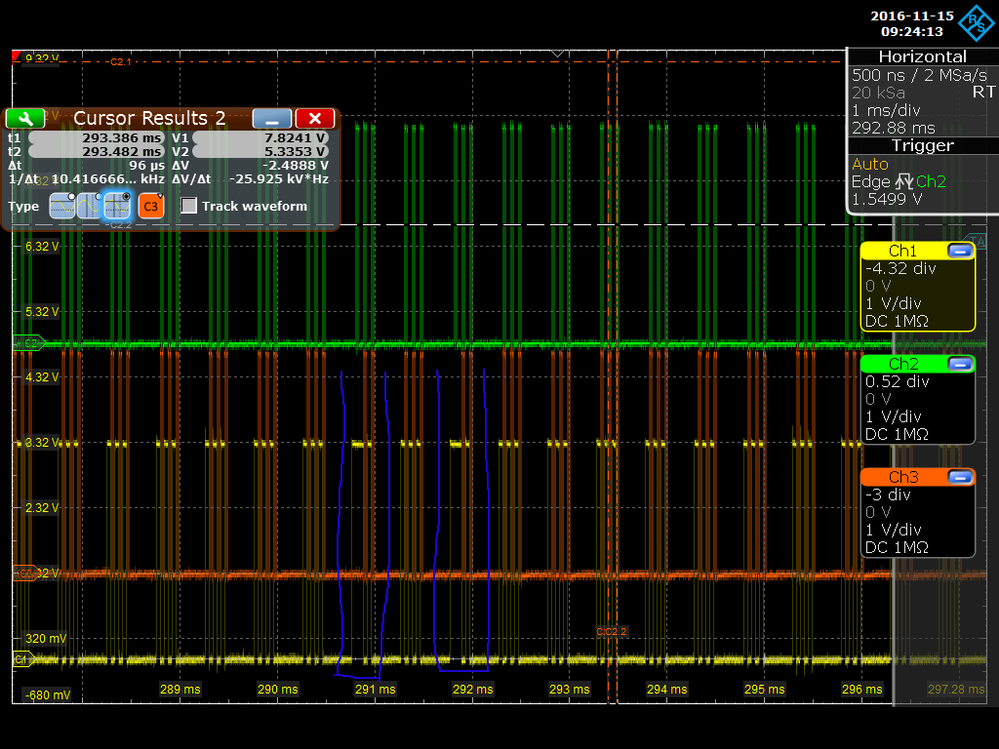

i have measured the flexpwm1_pwmx0, ctu0trigout, ctu1trigout( flexpwm0_pwmx0 not measured because the limit of the board)

both pics are Ch1: flexpwm1_pwmx0 Ch2: ctu0trigout Ch3:ctu1trigout

this is the first pic, it seems that flexpwm1's first cycle didn't wor well. my configuration is that the period is 80us and val0=val1/2 (both pwm0&1 are the same)

the second pic i set flexpwm1 INIT_SEL=0 (local sync cause initilation),

p_PWM->SUB[nCH].CTRL2.B.INIT_SEL = 3; /* 11 = EXT_SYNC causes initialization */

----->p_PWM->SUB[nCH].CTRL2.B.INIT_SEL = 0; /* 11 = EXT_SYNC causes initialization */

Another strange thing is i have set the etimer to count 24 triggers(as pic below), but it seems only 12 trigger will cause the interrupt, i have checked the settings and find no reason? can you help me for that, thank you very much!

PS: my program process is :

flexpwm0&1 trig ctu0&1

ctu0&1 trig adc&etimer

dma move adc data to ram and etimer count trig number and when number satisfy then stop flexpwm0&1

cycle again

the source code has attached.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

if i choose FlexPWM_x OUT_TRIG0_0 as CTU_x_TGSISR source(in the previous experiment FlexPWM_x PWMX0 was chosed as the CTU_x_TGSISR source) then the first cycle will trigger ok. But the pwmx0 still seems do not work well on the first cycle. you can see the pic below

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

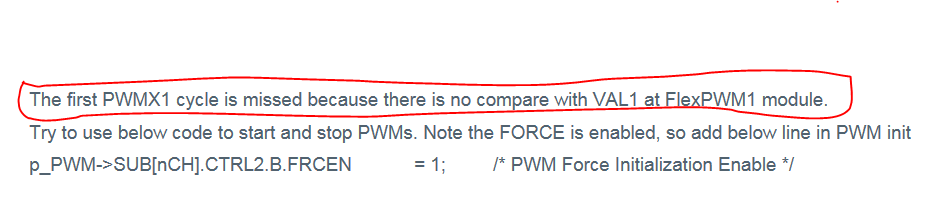

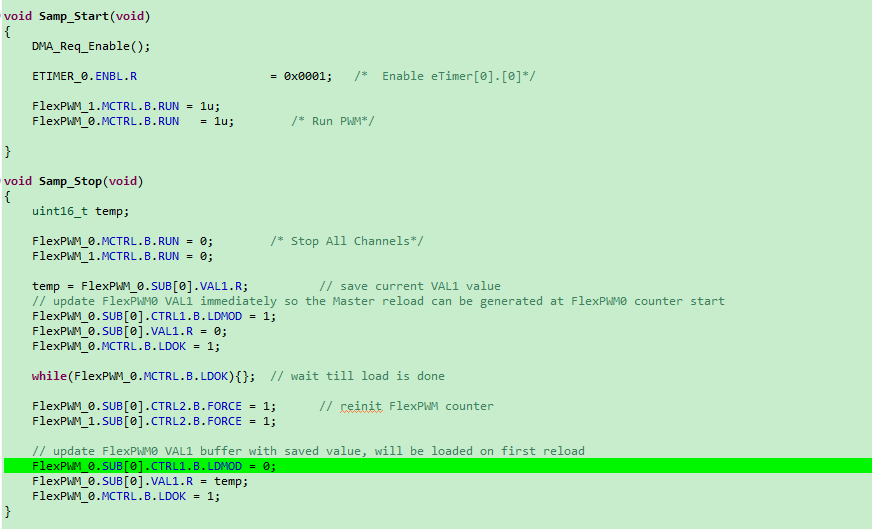

The first PWMX1 cycle is missed because there is no compare with VAL1 at FlexPWM1 module.

Try to use below code to start and stop PWMs. Note the FORCE is enabled, so add below line in PWM init

p_PWM->SUB[nCH].CTRL2.B.FRCEN = 1; /* PWM Force Initialization Enable */

void Samp_Start(void)

{

uint32_t i;

DMA_Req_Enable();

ETIMER_0.ENBL.R = 0x0001; /* Enable eTimer[0].[0]*/

FlexPWM_1.MCTRL.B.RUN = 1u; // start FlexPWM1 first so it can be synchronized by FlexPWM0

FlexPWM_0.MCTRL.B.RUN = 1u; /* Run PWM*/

}

void Samp_Stop(void)

{

uint16_t temp,i;

FlexPWM_0.MCTRL.B.RUN = 0; /* Stop All Channels*/

FlexPWM_1.MCTRL.B.RUN = 0;

temp = FlexPWM_0.SUB[0].VAL1.R; // save current VAL1 value

// update FlexPWM0 VAL1 immediately so the Master reload can be generated at FlexPWM0 counter start

FlexPWM_0.SUB[0].CTRL1.B.LDMOD = 1;

FlexPWM_0.SUB[0].VAL1.R = 0;

FlexPWM_0.MCTRL.B.LDOK = 1;

while(FlexPWM_0.MCTRL.B.LDOK){}; // wait till load is done

FlexPWM_0.SUB[0].CTRL2.B.FORCE = 1; // reinit FlexPWM counter

FlexPWM_1.SUB[0].CTRL2.B.FORCE = 1;

// update FlexPWM0 VAL1 buffer with saved value, will be loaded on first reload

FlexPWM_0.SUB[0].CTRL1.B.LDMOD = 0;

FlexPWM_0.SUB[0].VAL1.R = temp;

FlexPWM_0.MCTRL.B.LDOK = 1;

}

Seems this help, but it would be better to use PWMA or PWMB instead of PWMX as the edge will not be lost.

For the eTimer trigger count issue; this looks really strange, let me some time to check this too.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i want to know what does that mean"no compare with VAL1 at FlexPWM1 module", why no compare?

Thank you very much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For a eTimer counting, this is because you have measured CTU_EXT_OUT signal, which is toggled at each CTU trigger.

However the CTU’s ETIMER0_TRG signal is just single pulse (1 CTU clock) at each CTU trigger, so you have each time 2 edges on single CTU_EXT_OUT toggle.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Peter, Thank you very much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Because on subsequent PWM start both modules are not synchronized. There is no reload at PWM0 start at this point.

And because the PWMs are not started at the same time, in your code PWM0 starts first, the PWM0 cycle (VAL1 compare) ends sooner then it is on PWM1. Master reload is issued on this end of PWM0 cycle. PWM1 counter reinits, but there was no VAL1 compare in fact, that’s why there is missing falling edge. From now both PWMs are synchronized , but you do not see rising edge as the output is high still. You can see falling edge on second PWM cycle.

If the code I sent does not work, try to add some delay between PWM1 and PWM0 start.

Still I think a usage of PWMA or PWMB leads brings better functionality, but it depends if your application could use that.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

i have tried your seetings, as you can see below

but it seems did not ok. you can see there are some miss(blue part)