- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- How do I get CAN Rx interrupts to fire on an MPC5668G when the FIFO is enabled?

How do I get CAN Rx interrupts to fire on an MPC5668G when the FIFO is enabled?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How do I get CAN Rx interrupts to fire on an MPC5668G when the FIFO is enabled?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

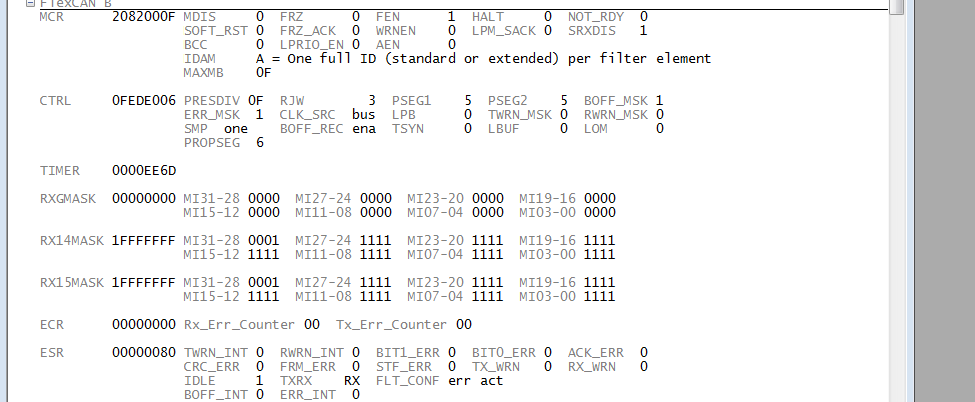

As soon as the FEN bit is set in CANx MCR the Rx Interrupts stop firing. We are using a port of MQX though I don't believe that to be the issue. All the registers look OK. I have reserved the lower 8 MBs (0 - 7) for Rx and moved the Tx MBs up. Tx works fine but no amount of coxing gets it to work. I'm now almost at register level:

CAN_B.MCR.B.FRZ = 1;

CAN_B.MCR.B.HALT = 1;

while(CAN_B.MCR.B.FRZACK == 0){};

CAN_B.MCR.B.FEN = 1;

CAN_B.MCR.B.HALT = 0;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks again. I now believe it's a bug in the MQX FLEXCAN_Install_isr routine. I will post when we have confirmed this

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

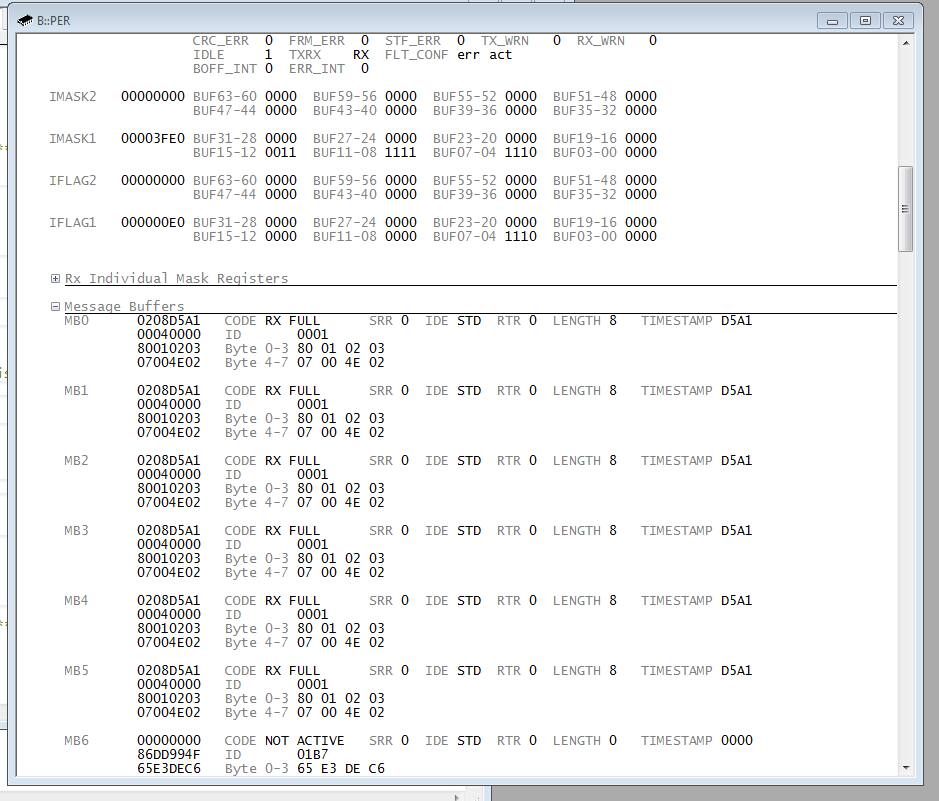

Please see another register screen shot. I must say it is starting to feel like a silicon bug. I am not convinced that interrupts actually work when FEN is set

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for that. I had previously downloaded that code and I'm afraid it didn't solve the problem as it polls the CAN. Firstly, we do not use message masks. We have no need since the bus is entirely private and we wish to receive everything on it. I can see MBs 0 to 5 filling up as expected. I have enabled interrupt 5 and I can see the request being set in the IFLAG register. The problem is then that the interrupt never fires.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If the FIFO is enabled the memory area from 0x80 to 0xFC (which is normally occupied by MBs 0 to 7) is used by the reception FIFO engine. The 8-entry ID table from FIFO is scanned first and then, if a match is not found within the FIFO table, the other MBs are scanned. When the frame is received, it is temporarily stored in a SMB. If a matching ID is found in the FIFO table or in one of the regular MBs, the contents of the SMB are transferred to the FIFO or to the matched MB.

There are following rules for message filtering for different FlexCAN module configuration:

- a) When MCR[FEN]=0, no RX FIFO

MCR[BCC]=0: MB0-MB64 use RXGMASK except MB14 uses RX14MASK and MB15 used RX15MASK

MCR[BCC]=1: MB0-MB64 use RXIMR0-RXIMR64

- b) When MCR[FEN]=1, RX FIFO used

MCR[BCC]=0: ID0-ID5 use RXGMASK, ID6 uses RX14MASK, ID7 uses RX15MASK

MB8-MB64 use RXGMASK except MB14 uses RX14MASK and MB15 used RX15MASK

MCR[BCC]=1: ID0-ID7 uses RXIMR0-RXIMR7, MB8-MB64 use RXIMR8-RXIMR64

Flags are set in following way when FIFO is enabled. The 8 least significant interrupt flags (BUF7I–BUF0I) is changed to support the FIFO operation. BUF7I, BUF6I and BUF5I indicate operating conditions of the FIFO, while BUF4I to BUF0I are not used. In details

- BUF5I - Buffer MB5 Interrupt or Frames available in FIFO.

- BUF6I - Buffer MB6 Interrupt or FIFO Warning. Four frames have accumulated in the FIFO.

- BUF7I - Buffer MB7 Interrupt orFIFO Overflow. The FIFO is full and subsequent frames arenot accepted until the CPU creates space in the FIFO by reading one or more frames. While theFIFO is full, the frames are only received if they are matched with another MB (MB8-MB63).

The 2nd word in the FIFO structure (0x84 ID Standard/Extended) represents the ID of received frame when frame is read (accessing an MB in the 0x80 address) from the RX FIFO.

The simple MPC5668G RXFIFO example can be found at

http://www.nxp.com/webapp/sps/download/license.jsp?colCode=MPC5668X-FLEXCAN-TX2RXFIFO

BR, Petr