- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- IPU Color video displayed in b/w

IPU Color video displayed in b/w

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IPU Color video displayed in b/w

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We're trying to use an SCM-i.MX6DQ IPU synchronous display flow to output a video clip from Memory to an ADV7391 encoder. The clip is YUV 4:2:2.

We've modified the Device Tree to output the 8-bit parallel interface and 27MHz clock.

Couple of issues:

1) IDMAC channel 23 is enabled and displaying the console. We want channel 23 to output the video only.

2) IDMAC channel 27 is initialized when using v4l2 and displays the video, and is then overlayed onto Channel 23.

3) Channel 27 output is black and white only. (See attached video clips) We are sending the first clip here: YUV Sequences with "/unit_tests/mxc_v4l2_output.out -ih 144 -iw 176 akiyo_qcif.yuv"

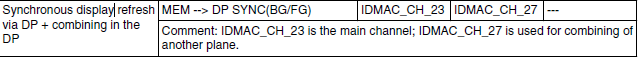

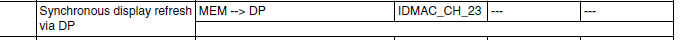

The IDMAC channels follow this flow:

But we want this:

How do we configure the IDMAC channels to display properly when launching V4L2? Is there a CPMEM configuration that needs to change?

*****CPMEM status for IDMAC channel 23****

--Word0@0x27005C0--

XV Virtual Coordinate[9:0]: 0000000000

YV Virtual Coordinate[18:10]: 000000000

YB inner Block Coordinate[31:19]: 0000000000000

XB inner Block Coordinate[43:32]: 000011110011

New Sub Block[44]: 0

Current Field[45]: 0

Scroll X counter[57:46]: 000000000000

Scroll Y counter[68:58]: 00000000000

Number of Scroll[78:69]: 0000000000

Scroll Delta X[85:79]: 0000000

Scroll Max[95:86]: 0000000000

Scrolling Configuration[96]: 0

Scrolling Enable[97]: 0

Scroll Delta Y[104:98]: 0000000

Scroll Horizontal Direction[105]: 0

Scroll Vertical Direction[106]: 0

Bits Per Pixel[109:107]: 011

Decode Address Select[111:110]: 00

Access Dimension[112]: 0

Scan Order[113]: 1

Band Mode[116:114]: 000

Block Mode[118:117]: 00

Rotation[119]: 0

Horizontal Flip[120]: 0

Vertical Flip[121]: 0

Threshold Enable[122]: 0

Conditional Access Polarity[123]: 0

Conditional Access Enable[124]: 0

Frame Width[137:125]: 0001011001111

Frame Height[149:138]: 000111100110

End of Line interrupt[150]: 0

--Word1@0x27005E0--

Ext Mem Buffer 0 Addr[28:0]: 00011100000100000000000000000

Ext Mem Buffer 1 Addr[57:29]: 00011100000100000000000000000

Interlace Offset[77:58]: 00000000000010110100

Number of Pixels in Whole Burst Access[84:78]: 0011111

Pixel Format Select[88:85]: 0111

Alpha Used[89]: 0

Alpha Channel Mapping[92:90]: 000

AXI Id[94:93]: 00

Threshold[101:95]: 0000000

Stride Line[115:102]: 00101100111111

Width0[118:116]: 100

Width1[121:119]: 101

Width2[124:122]: 100

Width3[127:125]: 111

Offset0[132:128]: 00000

Offset1[137:133]: 00101

Offset2[142:138]: 01011

Offset3[147:143]: 10000

Select SX SY Set[148]: 0

Conditional Read Enable[149]: 0

Decode Address Select bit[2][150]: 0

*****CPMEM status for IDMAC channel 27****

--Word0@0x27006C0--

XV Virtual Coordinate[9:0]: 0000000000

YV Virtual Coordinate[18:10]: 000000000

YB inner Block Coordinate[31:19]: 0000000000000

XB inner Block Coordinate[43:32]: 000011110000

New Sub Block[44]: 0

Current Field[45]: 0

Scroll X counter[57:46]: 000000000000

Scroll Y counter[68:58]: 00000000000

Number of Scroll[78:69]: 0000000000

Scroll Delta X[85:79]: 0000000

Scroll Max[95:86]: 0000000000

Scrolling Configuration[96]: 0

Scrolling Enable[97]: 0

Scroll Delta Y[104:98]: 0000000

Scroll Horizontal Direction[105]: 0

Scroll Vertical Direction[106]: 0

Bits Per Pixel[109:107]: 011

Decode Address Select[111:110]: 00

Access Dimension[112]: 0

Scan Order[113]: 1

Band Mode[116:114]: 000

Block Mode[118:117]: 00

Rotation[119]: 0

Horizontal Flip[120]: 0

Vertical Flip[121]: 0

Threshold Enable[122]: 0

Conditional Access Polarity[123]: 0

Conditional Access Enable[124]: 0

Frame Width[137:125]: 0001011001111

Frame Height[149:138]: 000111011111

End of Line interrupt[150]: 0

--Word1@0x27006E0--

Ext Mem Buffer 0 Addr[28:0]: 00011100101000000000000000000

Ext Mem Buffer 1 Addr[57:29]: 00011100101010101000110000000

Interlace Offset[77:58]: 00000000000010110100

Number of Pixels in Whole Burst Access[84:78]: 0011111

Pixel Format Select[88:85]: 1010

Alpha Used[89]: 0

Alpha Channel Mapping[92:90]: 000

AXI Id[94:93]: 00

Threshold[101:95]: 0000000

Stride Line[115:102]: 00101100111111

Width0[118:116]: 000

Width1[121:119]: 000

Width2[124:122]: 000

Width3[127:125]: 000

Offset0[132:128]: 00000

Offset1[137:133]: 00000

Offset2[142:138]: 00000

Offset3[147:143]: 00000

Select SX SY Set[148]: 0

Conditional Read Enable[149]: 0

Decode Address Select bit[2][150]: 0

Thank you in advance! Let me know if more information is needed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Steven

please check patches on

Patch to Support BT656 and BT1120 Output For i.MX6 BSP

for custom modifications may be recommended to apply to

NXP Professional Services as they are not supported in official nxp bsps:

http://www.nxp.com/support/nxp-professional-services:PROFESSIONAL-SERVICE

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------