- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- SWD additional pullup/pulldown resistor when the GPIO already has one

SWD additional pullup/pulldown resistor when the GPIO already has one

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SWD additional pullup/pulldown resistor when the GPIO already has one

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I might have more chance for my question in a new thread. The question was initially raised by IanB in this message: https://community.nxp.com/message/752591?commentID=752591#comment-752591 :

Unlike Mike, I'm using a device which shares its serial wire pins with GPIO. If the pull-up is enabled in IOCON as its default condition out of reset, doesn't it have a pull-up? Could you please clarify.

I had the same question myself and found this answer in Design Consideration for Debug https://community.nxp.com/thread/388998 :

Some MCUs do not include internal pull-up or pull-down resistors on JTAG/SWD pins. You will need to review the datasheet for the specific MCU being used to confirm. Where internal resistors are not provided, these should be added externally onto your board as detailed above. You may use resistors between 10K and 100K for these signals. This will prevent the signals from floating when they are not connected to anything. Failure to do this will lead to, at best, unreliable debug connections, or more likely no ability to debug at all.

If an internal resistor is provided for a pin by the MCU, then an external resistor is not required for that pin. But if external resistor is provided in such cases, then it must match that provided internally by the MCU.

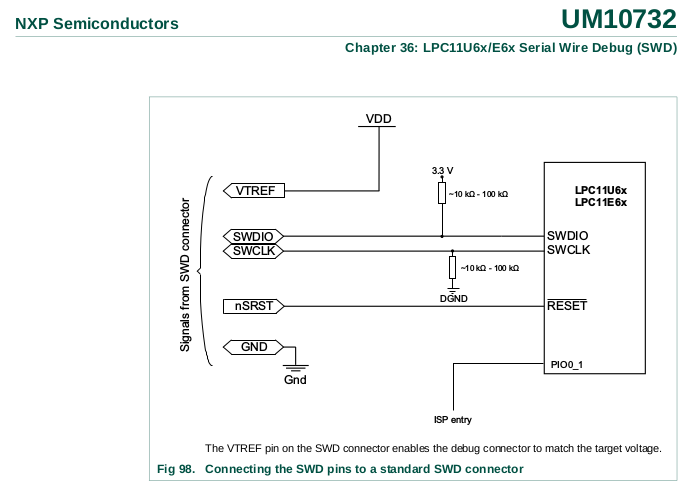

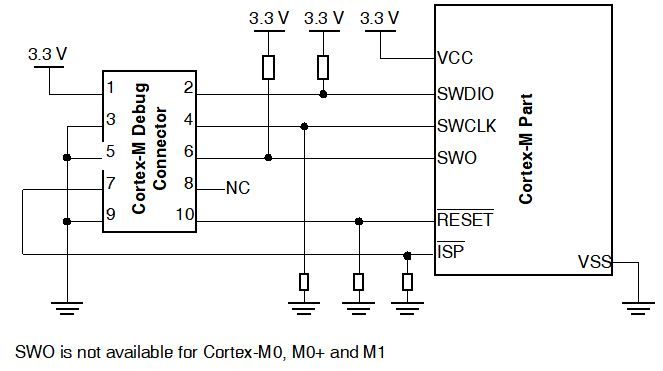

But later on, I found in the LPC11U6x User Manual and Data sheet that SWDIO and SWCLK pins have an internal pull-up for SWDIO and pull-down for SWCLK by default. But both documents contain a diagram that shows the recommendation to add a pull-up and pull-down resistors. And the value of these resistors do not necessary match the internal MCU...

So what should we do for LPC11U6x?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

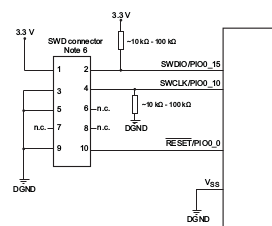

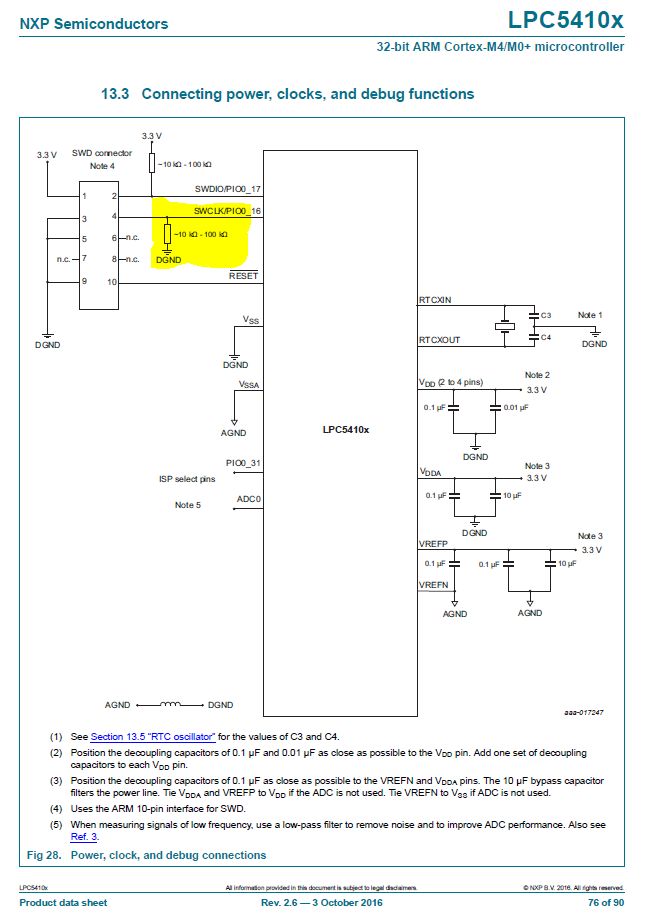

Similar problem with the LPC54102 (LPC5410x Series)

Datasheet page 76: (use external pull-down on SWCLK)

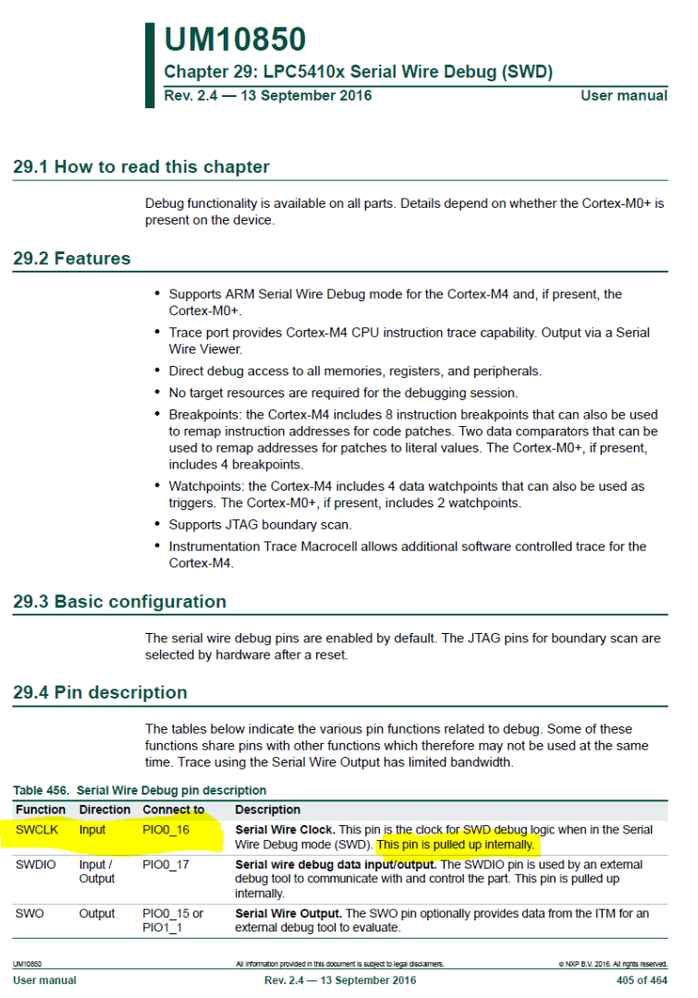

User Manual UM10850 of LPC5410x: (internal pull-up on SWCLK)

This two documents clearly conflict each other!

The datasheet recommends to use a pull-down on the SWCLK while the user manual states that there is an internal pull-up.

This leads to higher standby currents due to the two opposite resistors on the SWCLK!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is my understanding based on all the information available.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes - its quite clearly nonsense, but NXP won't admit it! I do note that the pull-down resistor has been left of the connection diagram in later device (LPC15xx, for instance).

It's worse than just the current through the resistors: if one happens to choose a pull-down which is the same value as the internal pull-up, the the inputs transistors are both biassed on, and current flows through them - much more current than flows through the resistors; and the noise-immunity on the pin is completely destroyed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Olivier Martin ,

1. If the pull-up is enabled in IOCON as its default condition out of reset, doesn't it have a pull-up?

Yes.

2. Yes, it's recommended to add an external resistor to the WDIO and SWCLK pins when design the debug interface.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------