- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Software Forums

- :

- Processor Expert Software

- :

- Big Problems with ADCs generated code on KV31P100M120

Big Problems with ADCs generated code on KV31P100M120

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have been fighting issues for a while on this processor and the dev platform TWR-KV31F120M attempting to use the two ADC cores on the above processor using the ADC_LDD bean. To me it appears this "bean" is incomplete at best. Whatever the case, it is producing inconsistent non-working code, especially if I change the setting for "Number of conversions" or "Result Type".

Problem 1: The Trigger portion of the GUI for ADC_LDD does nothing with the SIM_SOPT7 register, which is supposed to route the trigger signals from the selected timer/peripheral to the ADC core to trigger the conversions. This I found I had to manually add the SIM bean to my project, and manually edit the fields so the SIM_SOPT7 register was properly set up. Otherwise the ADC_LDD leaves this register at defaults and wont route any trigger signals to the ADC cores. Once the SIM bean is added to the project, it begins to interact with the Trigger settings of the ADC_LDD bean, and I had the loop triggering functioning... for a short while.

Problem 2: Even though I have the SOPT7 register properly setup, I only can occasionally get the ADC events for conversion complete to actually occur. At one point I had things working with Number of Conversions set to 1, and timing working, etc. While getting regular conversions, I ran into a problem where I was getting 8-bit signed values out left-shifted into position even though I had 16-bits signed selected. I went in and changed number of conversions to see if averaging had something to do with my problem. After this Number of Conversions change, I no longer get conversion complete events, the ADC bean claims things are always busy, even when I revert my settings.

It should not be timing, as I am only attempting to sample at a 1kHz rate to get things started before I turn up the speed.

Problem 3: I started playing with the settings trying to figure out the 8-bit problem, and realized the "Result Type" dropdown is not behaving correctly. I select "signed 16 bits, left justified", and click the down arrow again and I wind up with a different selection than what I asked for highlighted. It does not give me any confidence that what I selected is actually being generated. In fact it does appear to be quite incorrect and giving me 8-bit results instead of the 16-bits I am asking for.

So this combination of problems has me running around in circles simply trying to get regular sample timings on both ADC cores based on the PIT timer. The goal here early in this project is to use the two ADCs as a "scope" for debug purposes before utilizing them for a decision making process.

What is very frustrating is that I had it working, and now it doesn't even with reverted settings.

What is the news with this processor and PE? Is there ongoing development and support, or am I getting killed by this NXP acquisition? Before this project, I never had any significant problems with PE.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

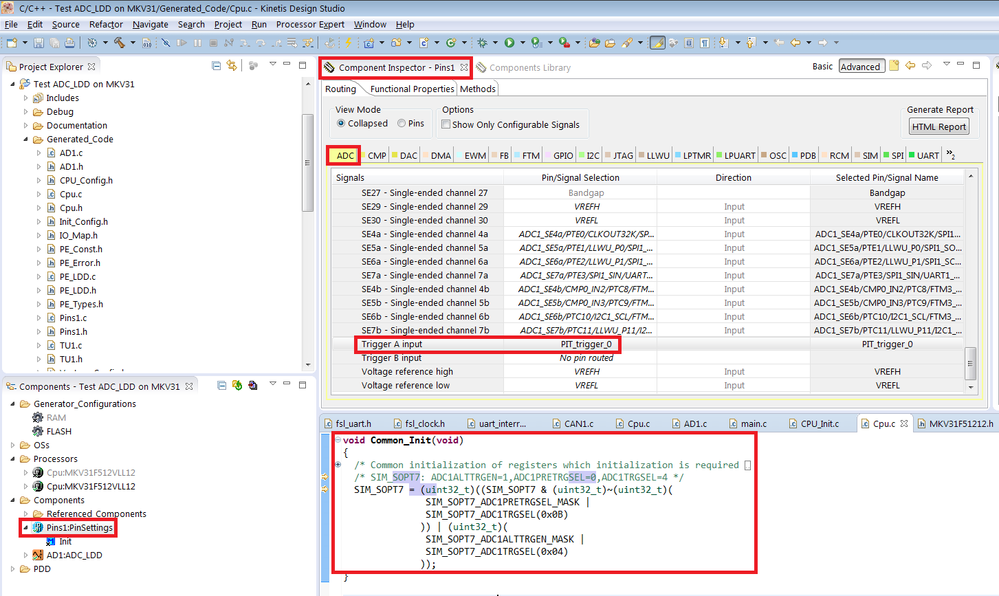

the development team has provided a workaround for this issue. You can use PinSettings component for routing of trigger signals, i.e. you can select the trigger source of the ADC (on the ADC tab) in the PinSettings. In this case the source code (SIM_SOPT7 register initialization) is properly generated in the Common_Init() function (Cpu.c generated source code file).

See the example on the following screenshot:

Best Regards,

Marek Neuzil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As an FYI, it does look like PE is generating the correct code for Result Type, and the register is set properly for the bit depth of the conversion (0x6C on ADCx_CFG1).

I did find the problem with the lack of triggering, and that is due to the timing selection dialog allowing ALTCLK2. If I force the clock dialog to use the Bus Clock, it of course limits my clock selections, but now I consistently have triggers since the ADC core has clocks. This seems to be the root cause of why changing averaging and other options which updated the timing would suddenly stop working. It wasn't they other settings, but these alternate clock sources.

I still have to manually deal with SOPT7 though... this one caused me a few headaches.

Also note that the setting for Long Sample Time Select is not being generated, whether I have High Speed Conversion selected or not.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Mark,

I have verified the issue and the ADC_LDD (Processor Expert for Kinetis) contains a defect in the driver. The SIM_SOPT7 is not configured. I have reported this issue to the responsible development team.

I have also checked the using of the Long Sample Time Select bit but it seems that it works properly. This bit is controlled by selection of the value in the Sample Time property.

Best Regards,

Marek Neuzil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

the development team has provided a workaround for this issue. You can use PinSettings component for routing of trigger signals, i.e. you can select the trigger source of the ADC (on the ADC tab) in the PinSettings. In this case the source code (SIM_SOPT7 register initialization) is properly generated in the Common_Init() function (Cpu.c generated source code file).

See the example on the following screenshot:

Best Regards,

Marek Neuzil