- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- deadtime on 100%duty of flexPWM in MPC5744P

deadtime on 100%duty of flexPWM in MPC5744P

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

deadtime on 100%duty of flexPWM in MPC5744P

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi everyone,

i found a problem about 100% duty of flexPWM in MPC5744P.

when initial the flexPWM, i set below:

#define FlexPWM0_DTSRCSEL 0x0000u

#define FlexPWM0_MCTRL 0xff00u //PWM45 ( PWM submodule ) is used to generate complementary PWM pair.

#define FlexPWM0_CTRL2_sub0 0xc2A0u //PWMA and PWMB form a complementary PWM pair.

#define FlexPWM0_INIT_sub0 0xF060u

#define FlexPWM0_VAL1_sub0 0x0FA0u //period is 8000

#define FlexPWM0_OCTRL_sub0 0x0610u //invert PWMA, invert PWMB

#define FlexPWM0_DTCNT0_sub0 112u //PWM A dead time

#define FlexPWM0_DTCNT1_sub0 112u //PWM B dead time

then i set the "FlexPWM0_VAL4_sub0 = 0xF060u;" and "FlexPWM0_VAL5_sub0 = 0x0FA0u ;"

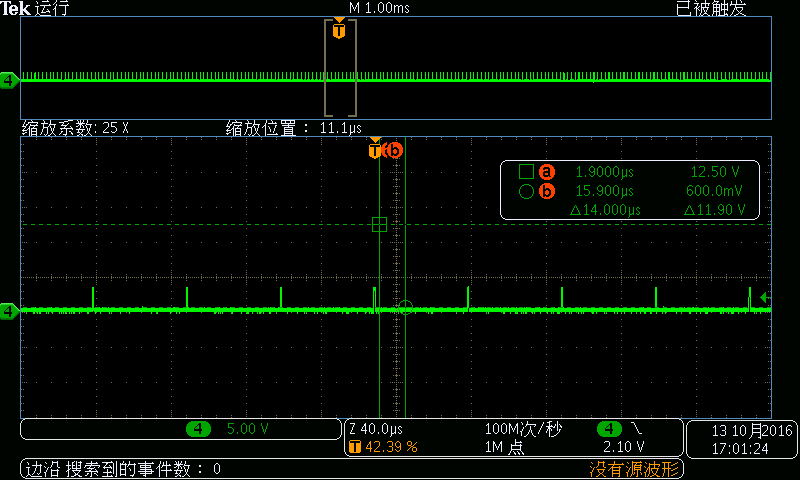

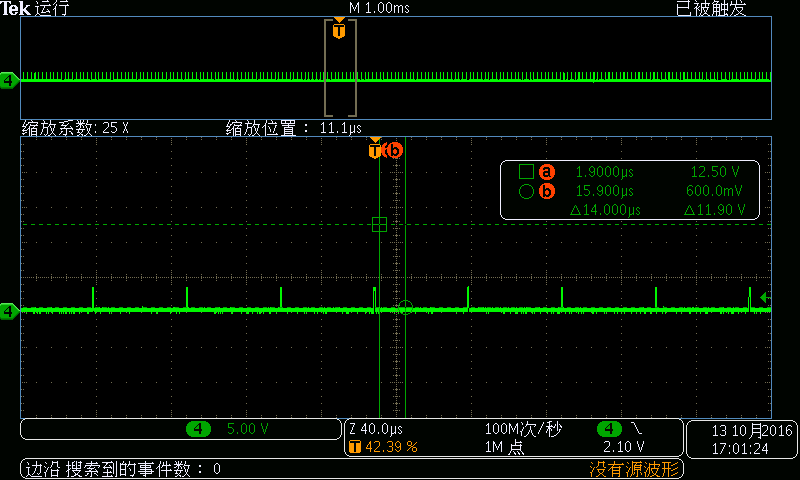

in my opinion, i think the PWMB will output 100% duty and PWMA will output 0% duty, but i strangely found that PWMB output 100% duty but PWMA output not 0% duty. the PWMA scope like below:

i measured the high level time pluse is equal to the deadtime set in FlexPWM0_DTCNT0_sub0. to verify the relationship between FlexPWM0_DTCNT0_sub0 and PWMA, i set "FlexPWM0_DTCNT0_sub0 = 0" and then the PWMA can output 0% duty successfully.

in this case, my problem is three:

1. why PWMA cannot complementary from PWMB all the time?

2. when i set PWMB 100% duty, how the relationship between FlexPWM0_DTCNT0_sub0 and PWMA appeared?

3. if the "FlexPWM0_DTCNT0_sub0 = 0", is there any risk exists in my high bridge and low bridge motor control circle application?

please help me , thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

With your setting

#define FlexPWM0_INIT_sub0 0xF060u

#define FlexPWM0_VAL1_sub0 0x0FA0u

the period is 8000+1.

Using the FlexPWM0_VAL4_sub0 = 0xF060u;" and "FlexPWM0_VAL5_sub0 = 0x0FA0u you do not have 100% duty cycle on PWM45, but there is low pulse with length of single PWM clock. That’s why you see such pulse on PWMA after deadtime insertion logic. Look at Figure 40-148. "Deadtime Insertion and Fine Control Logic" of the device RM to know how deadtime is inserted.

Set FlexPWM0_VAL5_sub0 = 0x0FA1u to get 100% duty.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi petr,

thanks for your response.

but i have tested my project follow your idea, the problem still exists.

can you give me a demo project, that really realize the 100% duty in flexPWM0_sub0/2/3 with a complementary PWM pair of PWMA and PWMB? and the demo project is better to use VAL45 to make complementary.

may be there are some other reason coursing my problem. i can compare your demo project with mine to find out it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

try this...

static void FlexPWM_Init(void)

{

/* Submodule 0 Initialisation */

FlexPWM_0.OUTEN.R = 0x110; // enable A and B outputs on submodule 0

FlexPWM_0.SUB[0].CTRL1.R = 0x0400; // full cycle reload, every opportunity,IPBus/1

FlexPWM_0.SUB[0].CTRL2.R = 0x8080; // debug and force enable

FlexPWM_0.SUB[0].INIT.R = 0xF060; // PWM modulo

FlexPWM_0.SUB[0].VAL1.R = 0x0FA0; // PWM modulo

FlexPWM_0.SUB[0].VAL2.R = -200; // PWM A0 rising edge

FlexPWM_0.SUB[0].VAL3.R = 200; // PWM A0 falling edge

FlexPWM_0.SUB[0].VAL4.R = 0xF060; // PWM B0 rising edge

FlexPWM_0.SUB[0].VAL5.R = 0x0FA0+1; // PWM B0 falling edge

FlexPWM_0.SUB[0].DTCNT0.R = 112; // deadtime values

FlexPWM_0.SUB[0].DTCNT1.R = 112;

FlexPWM_0.SUB[0].OCTRL.R = 0x0610; //invert PWMA, invert PWMB

FlexPWM_0.SUB[0].DISMAP.R = 0x0000; // disable fault pin condition

FlexPWM_0.MCTRL.R = 0x1100; // PWM45 is used to generate complementary PWM pair.

// Submodule 0 PWM generator enabled

FlexPWM_0.SUB[0].CTRL2.B.FORCE = 1; // generate FORCE to take MCTRL[IPOL] effect

FlexPWM_0.MCTRL.B.LDOK = 0x1; // Load the PRSC bits of CTRL1 and the INIT, and VALx registers

// into a set of buffers

}