- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior Development Tools

- :

- When I use CodeWarrior8.8 to connect to the target board (mpc8377), there are the following errors:

When I use CodeWarrior8.8 to connect to the target board (mpc8377), there are the following errors:

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

When I use CodeWarrior8.8 to connect to the target board (mpc8377), there are the following errors:

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please try whether it would be helpful to use CodeWarrior JTAG configuration file to override RCW.

Please configure JTAG configuration file from Edit->Debug Version Settings->Remote Debugging->Edit Connection->Use JTAG configuration file.

Please use and modify the JTAG configuration file C:\Program Files (x86)\Freescale\CodeWarrior PA V8.8\PowerPC_EABI_Support\Initialization_Files\jtag_chains\837xRDB_rev10_HRCW_jtag.txt according to your target board. Please pay attention to RCWLR[COREPLL].

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

When the boot sequencer is enabled, the e300 core must be prevented from fetching boot code, by setting the core disable reset configuration word field(COREDIS) in RCWHR. If the e300 core is required to proceed the boot sequencer should enable boot vector fetch by clearing ACR[COREDIS].

Please check whether RCWHR[COREDIS] is set.

Please check whether RCWLR[COREPLL] is configured correctly.

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for your reply. RCWHR and RCWHL are not configured at the time of the connection.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please try whether it would be helpful to use CodeWarrior JTAG configuration file to override RCW.

Please configure JTAG configuration file from Edit->Debug Version Settings->Remote Debugging->Edit Connection->Use JTAG configuration file.

Please use and modify the JTAG configuration file C:\Program Files (x86)\Freescale\CodeWarrior PA V8.8\PowerPC_EABI_Support\Initialization_Files\jtag_chains\837xRDB_rev10_HRCW_jtag.txt according to your target board. Please pay attention to RCWLR[COREPLL].

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

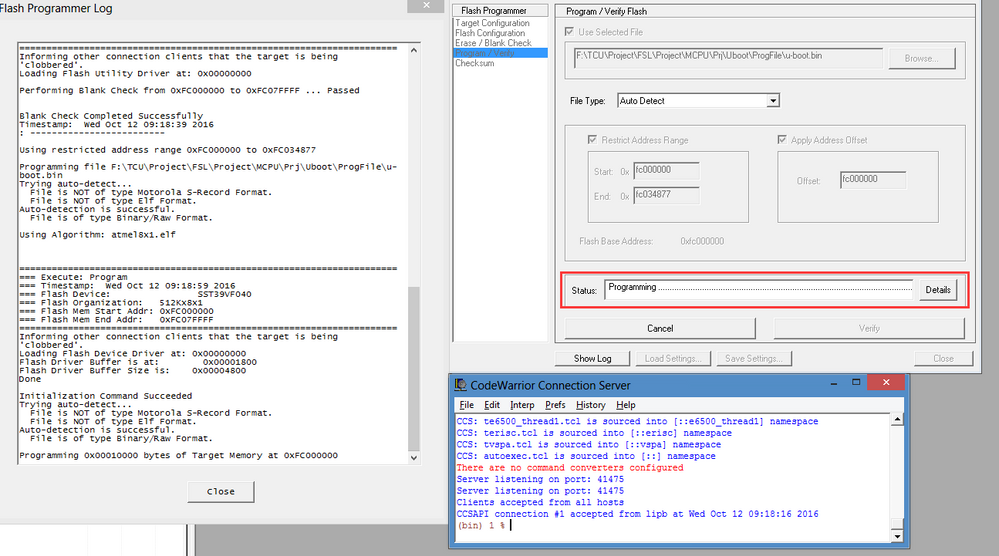

As you have described, I have been connected to the. I am in the NorFlash (SST39VF040) programming is the emergence of the following issues, Erase can be successful, programming failures, as shown below:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Would you please provide your CodeWarrior initialization file?

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The following is my CodeWarrior initialization file:

#setMMRBaseAddr 0xE0000000

writereg MBAR 0xFF400000

#change internal MMR base from 0xFF400000 (reset value) to 0xe0000000

writemem.l 0xFF400000 0xe0000000 # IMMRBAR = 0xe0000000

#setMMRBaseAddr 0xe0000000

writereg MBAR 0xe0000000

##############################################

# System Configuration - Local Access Windows

##############################################

# Local Bus Local Access Windows

#################################

# WINDOW 0 - NOR FLASH

writemem.l 0xE0000020 0xFC000000 # LBLAWBAR0 - begining at 0xfC000000

writemem.l 0xE0000024 0x80000019 # LBLAWAR0 - enable, size = 64MB

# WINDOW 1 - NAND FLASH -1GB

#writemem.l 0xE0000038 0xF8000000 # LBLAWBAR1 - begining at 0xFA000000

#writemem.l 0xE000003c 0x80000019 # LBLAWAR1 - enable, size = 64MB

# PCI Local Access Windows

#################################

# WINDOW 0

#writemem.l 0xE0000060 0x80000000 # PCILAWBAR0 - begining at 0x80000000

#writemem.l 0xE0000064 0x8000001C # PCILAWAR0 - enable, size =512MB

# DDR Local Access Windows

#################################

# WINDOW 0 - 1st DDR

writemem.l 0xE00000a0 0x00000000 # DDRLAWBAR0 - begining at 0x00000000

writemem.l 0xe00000a4 0x8000001b # DDRLAWAR0 - enable, size = 256MB

##############################################

# DDR Controller Configuration

##############################################

#DDRCDR

# hardware calibration, 150ohm, DDR2, DRQ

writemem.l 0xE0000128 0x40080000

#CLK_CNTL

# bit 0 = 1 - SS_EN address and command sent to the DDR source synchronously

# bit 5-7 = 2 - CLK_ADJST

writemem.l 0xE0002130 0x02000000

# CS0_BNDS

# bit 8-15 - starting address -0x0000_0000

# bit 24-31 - ending address - 0x0fff_ffff

writemem.l 0xe0002000 0x0000001f ;# first 256MB

# CS1_BNDS

# bit 8-15 - starting address -0x1000_0000

# bit 24-31 - ending address -0x1fff_ffff

#writemem.l 0xe0002008 0x00000000 ;# second 256MB

# CS0_CONFIG

writemem.l 0xe0002080 0x80010202

# CS1_CONFIG

#writemem.l 0xe0002084 0x80014102

# TIMING_CFG_0

writemem.l 0xE0002104 0x00220802

# TIMING_CFG_1

writemem.l 0xE0002108 0x3935D322

# TIMING_CFG_2

writemem.l 0xE000210C 0x231048C8

# TIMING_CFG_3

writemem.l 0xE0002100 0x00000000

# temporary disable the memory interface for reconfiguration

# DDR_SDRAM_CFG

writemem.l 0xE0002110 0x43000000

# DDR_SDRAM_CFG_2

writemem.l 0xE0002114 0x00001000

# DDR_SDRAM_MODE

writemem.l 0xe0002118 0x44500632 ;reference DDR datasheet

# DDR_SDRAM_MODE_2

writemem.l 0xE000211C 0x8000c000 ;reference DDR datasheet

# DDR_SDRAM_INTERVAL

writemem.l 0xe0002124 0x03CF0080

#delay before enable

sleep 1000

# enable the DDR memory controller

writemem.l 0xe0002110 0xc3000000

sleep 1000;#this is needed because of the D_INIT enable in DDR_SDRAM_CFG_2

##############################################

# Local Bus Interface (LBIU) Configuration

##############################################

# LCRR - Clock Ratio Register

writemem.l 0xE00050d4 0x80000004

### CS0 - 512K NorFLASH

writemem.l 0xe0005000 0xFC000801 # BR0 base address at 0xFc000000, port size 8 bit, GPCM, valid

writemem.l 0xe0005004 0xFFF80FF7 # OR0 512K flash size, 15 w.s., timing relaxed

### CS1 - 32MB NorFLASH

writemem.l 0xe0005008 0xFC081001 # BR0 base address at 0xFC080000, port size 16 bit, GPCM, valid

writemem.l 0xe000500c 0xFE000FF7 # OR0 32MB flash size, 15 w.s., timing relaxed

### CS2 - 1MB FPGA

writemem.l 0xe0005010 0xFE081001 # BR0 base address at 0xFE080000, port size 16 bit, GPCM, valid

writemem.l 0xe0005014 0xFFF00FF7 # OR0 1MB FPGA size, 15 w.s., timing relaxed

### CS3 - 1MB NVSRAM

writemem.l 0xe0005018 0xFE181001 # BR0 base address at 0xFE180000, port size 16 bit, GPCM, valid

writemem.l 0xe000501c 0xFFF00FF7 # OR0 1MB NVSRAM size, 15 w.s., timing relaxed

# LBCR - local bus enable

writemem.l 0xE00050d0 0x00000000

# LSRT - refresh timer #LPB DaiDing

writemem.l 0xE00050a4 0x3f000000

# MRTPR - refresh timer prescaler

writemem.l 0xE0005084 0x20000000

##############################################

# System configuration registers

##############################################

# SWCRR - Disable the watchdog timer

writemem.l 0xE0000204 0x00000000

writemem.l 0xE0000114 0x80000000 # SICRL

writemem.l 0xE0000118 0x00000002 # SICRH

###ANDmem.l 0xe0000118 0x00000003

#Enable Core in ACR - leave bits 10-11 as they are and zero all others

ANDmem.l 0xE0000800 0x00100000 #LPB

#writereg MSR

writereg MSR 0x3000 # machine check enable, exception vectors at 0x0000_0000

####################################################

# Enable PCI_CLK_OUT[0]

#writemem.l 0xE0000a04 0x80000000

####################################################

#writereg PC 0xFFF00100

Thanks.