- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- MK02FN64VLF10 UART Transfer Debug Problem

MK02FN64VLF10 UART Transfer Debug Problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MK02FN64VLF10 UART Transfer Debug Problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there,

I want to using uart sends character to the pc as following

/***************************************************************************

* Defines

**************************************************************************/

#define DEMO_UART UART1

#define BOARD_DEBUG_UART_BAUDRATE 115200

/***************************************************************************

* Variables

**************************************************************************/

uint8_t txbuff[] = "Uart polling example\r\nBoard will send back received characters\r\n";

uint8_t rxbuff[20] = {0};

/***************************************************************************

* Code

**************************************************************************/

int main(void){

uint8_t ch;

uart_config_t config;

/* Init board hardware*/

BOARD_InitPins();

BOARD_BootClockRUN();

/*

* config.baudRate_Bps = 115200U;

* config.parityMode = kUART_ParityDisabled;

* config.stopBitCount = kUART_OneStopBit;

* config.txFifoWatermark = 0;

* config.rxFifoWatermark = 1;

*/

UART_Init(DEMO_UART, &config, CLOCK_GetFreq(kCLOCK_CoreSysClk));

UART_WriteBlocking(DEMO_UART, txbuff, sizeof(txbuff) - 1);

while(1)

{

UART_ReadBlocking(DEMO_UART, &ch, 1);

UART_WriteBlocking(DEMO_UART, &ch, 1);

}

}

void BOARD_InitPins(void){

CLOCK_EnableClock(kCLOCK_PortA);

CLOCK_EnableClock(kCLOCK_PortB);

CLOCK_EnableClock(kCLOCK_PortC);

CLOCK_EnableClock(kCLOCK_PortD);

CLOCK_EnableClock(kCLOCK_PortE);

PORT_SetPinMux(PORTC, 3U, kPORT_MuxAlt3);

PORT_SetPinMux(PORTC, 4U, kPORT_MuxAlt3);

}

kCLOCK_CoreSysClk @40MHz

kCLOCK_BusClk @40MHz

FEE mode

void UART_GetDefaultConfig(uart_config_t *config)

{

assert(config);

config -> baudRate_Bps = 115200U;

config -> parityMode = kUART_ParityDisabled;

#if defined(FSL_FEATURE_UART_HAS_STOP_BIT_CONFIG_SUPPORT) && FSL_FEATURE_UART_HAS_STOP_BIT_CONFIG_SUPPORT

config -> stopBitCount = kUART_OneStopBit;

#endif

#if defined(FSL_FEATURE_UART_HAS_FIFO) && FSL_FEATURE_UART_HAS_FIFO

config -> txFifoWatermark = 0;

config -> rxFifoWatermark = 1;

#endif

config -> enableTx = false;

config -> enableRx = false;

}

but when using FRDM-K22F runs uart_polling_transfer.c but SYSTEM_CLOCK @40MHz, BUS_CLOCK @40MHz, also in FEE mode, it runs good.

How can i fix the problem, the mk02 also can output the right message?

Thanks in advance!

-Jack

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

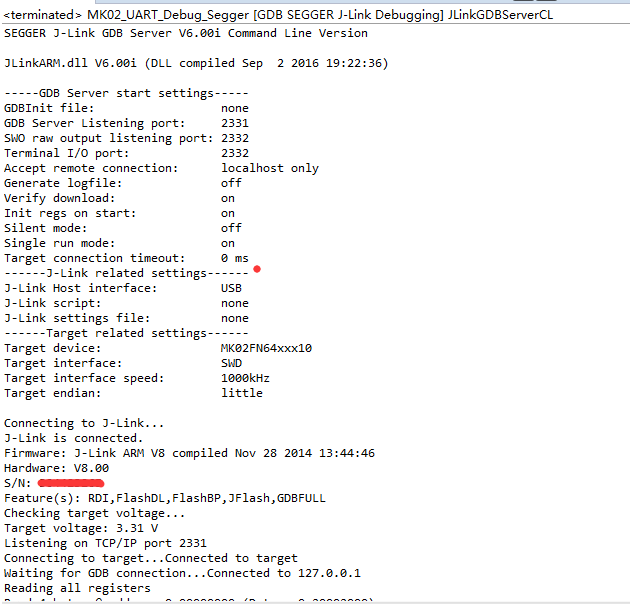

Hi Kerry,

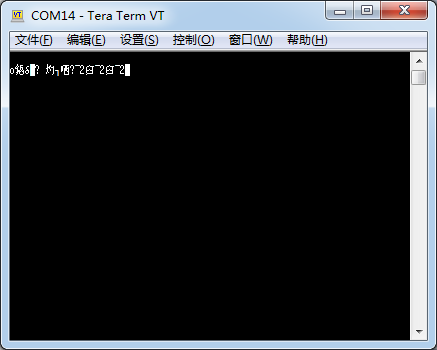

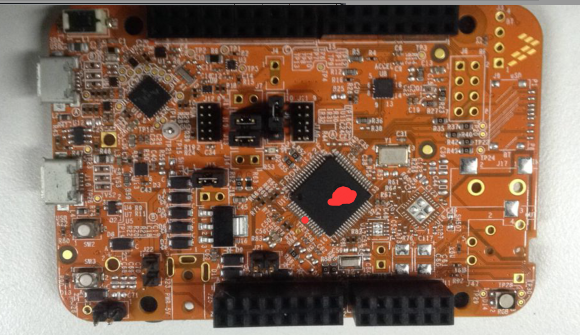

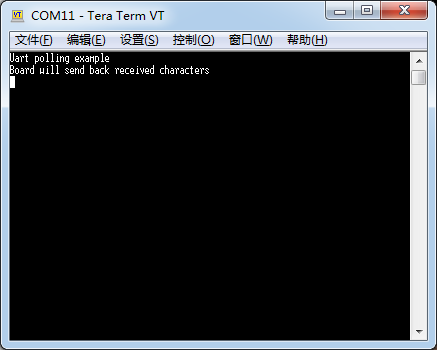

Thanks for your quick answer, but i load two sample. one is base on frdm-k22f, and another is base on mk02fn64vlf10. when core system @40MHz, frdm-k22f can send the right message to the tera term with 115200bps, but the mk02fn64vlf10 can not send the right one with 115200bps.

Due to we set the clock at 40MHz, and as caculated FRDM-K22F can send out the right message, but MK02FN64VLF10 can't

If MK02FN64VLF10 doesn't run at 40MHz, we also can not caculate the right one

U

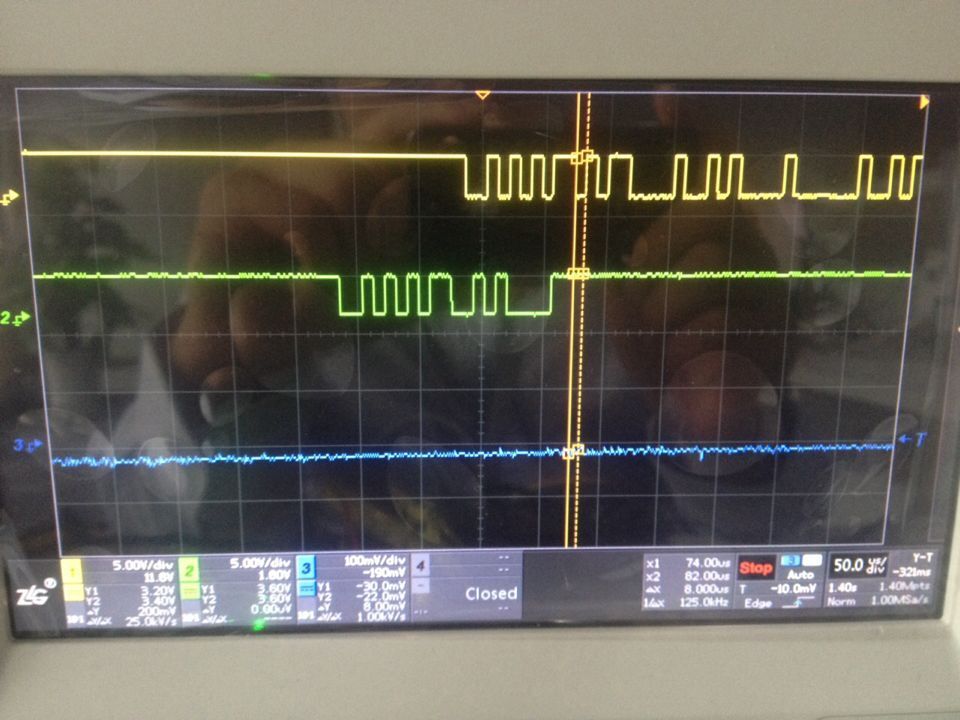

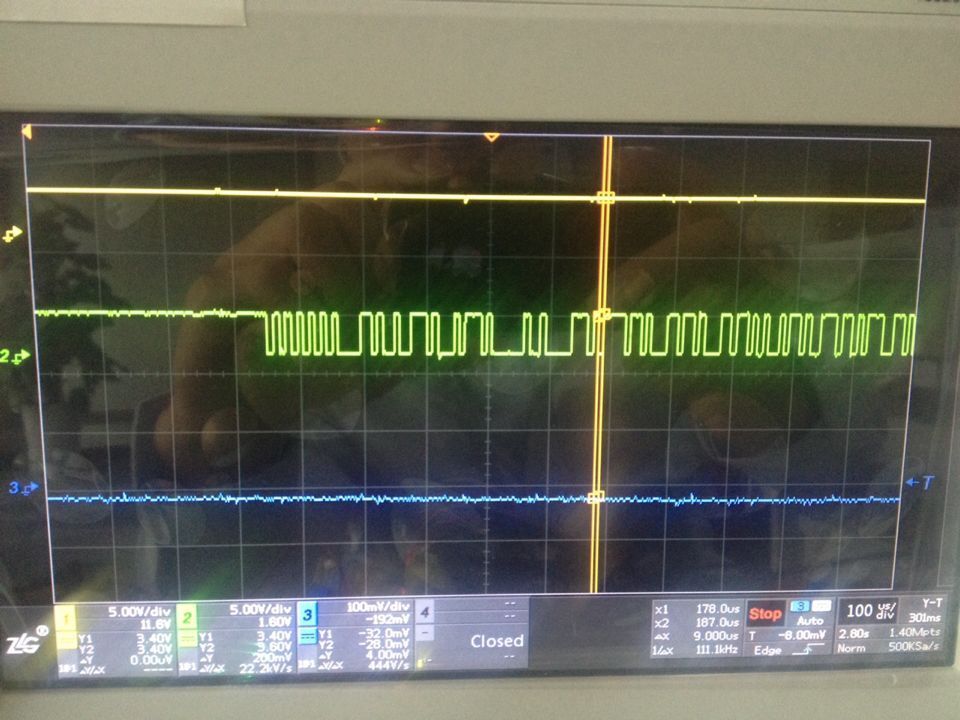

The 1st pic is from FRDM-K22F, the 2nd is from MK02FN64VLF10. both @115200bps

Need some more help, hope the 2nd one can send out right message!

Thanks in advance!

-Jack

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jack,

You receive the messy code, it is normally caused by the baud rate skew.

Normally, the baud rate deviation should smaller than 1.5%, otherwise the PC may receive the messy code.

So, please debug the code, and check the UARTx_BDH and UARTx_BDL, then calculate the baud rate

UART baud rate = UART module clock / (16 × (SBR[12:0] + BRFD)),

More details about the uart baud rate forum, please refer to chapter 40.4.3 Baud rate generation in the K02 reference manual.

Please calculate your real baud rate, and compare with 115200, is the baud rate deviation larger than 1.5%?

If yes, please reconfigure your UARTx_BDH and UARTx_BDL, to make sure the baud rate deviation should smaller than 1.5%.

Wish it helps you!

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

/* Calculate the baud rate modulo divisor, sbr*/

sbr = srcClock_Hz / (baudRate_Bps * 16);

/* Write the sbr value to the BDH and BDL registers*/

base->BDH = (base->BDH & ~UART_BDH_SBR_MASK) | (uint8_t)(sbr >> 8);

base->BDL = (uint8_t)sbr;

#if defined(FSL_FEATURE_UART_HAS_BAUD_RATE_FINE_ADJUST_SUPPORT) && FSL_FEATURE_UART_HAS_BAUD_RATE_FINE_ADJUST_SUPPORT

/* Determine if a fractional divider is needed to fine tune closer to the

* desired baud, each value of brfa is in 1/32 increments,

* hence the multiply-by-32. */

uint16_t brfa = (32 * srcClock_Hz / (baudRate_Bps * 16)) - 32 * sbr;

/* Write the brfa value to the register*/

base->C4 = (base->C4 & ~UART_C4_BRFA_MASK) | (brfa & UART_C4_BRFA_MASK);

#endif