- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Software Development Kit

- :

- Bug report: fsl_sai_edma ignores multichannel SAI module

Bug report: fsl_sai_edma ignores multichannel SAI module

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Bug report: fsl_sai_edma ignores multichannel SAI module

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It appears that fsl_sai_edma.c uses the static s_edmaPrivateHandle to maintain callbacks for EDMA, but it reserves the 0 index for TX and 1 index for RX, ignoring SAI modules with more than one tx/rx channel (example: the K24 I am using has 2 TX and 2 RX in one SAI module).

I used the FSL_FEATURE_SAI_CHANNEL_COUNT feature indicator to amend fsl_sai_edma (see attached solution)

Original Attachment has been moved to: fsl_sai_edma.c.zip

Original Attachment has been moved to: fsl_sai_edma.h.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi!

I'm trying to make this work with 2 TX channels but am having a hard time. I've replaced the fsl driver files with the ones attached to this thread and created 2 separate handlers for each TX channel but it still doesn't work.

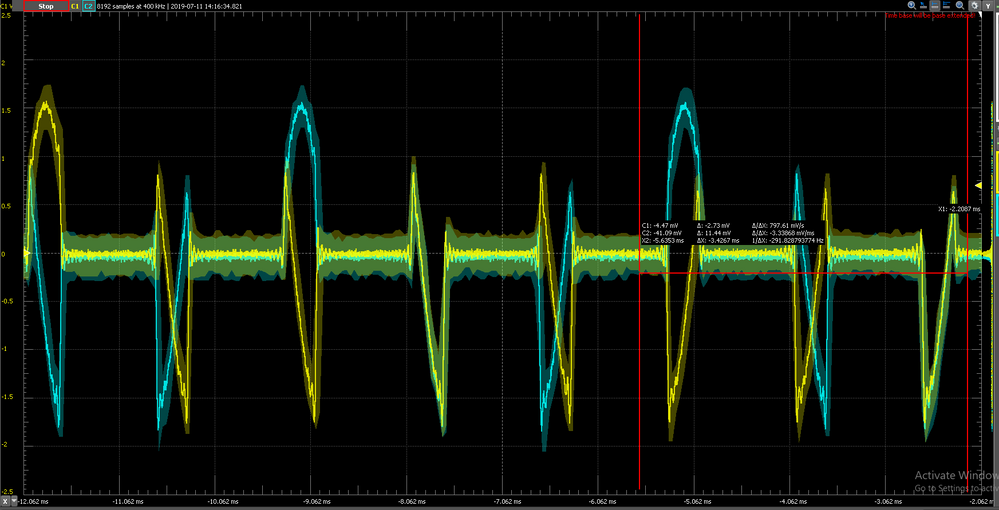

The closest thing I got to it working shown the result above (should have been a 1 kHz sine wave for each of the channels). I figured out that its only the first FIFO block is getting through, but further requests are being ignored until a new DMA transfer is submitted. I can easily make it work with one channel but ultimately the point is for these 2 channels to be working independently.

If you have any ideas about what may be happening, please let me know :smileyhappy:.

Thanks for your time!

Henrique

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Additionally, in SAI_RxSetFormat, the active channels are zeroed out every time it's called:

base->RCR3 &= ~I2S_RCR3_RCE_MASK;

This makes it impossible to run 2 channels. With my above fix to fsl_sai_edma, as well as deleting this line zeroing RCR3, I have 2 RX channels working simultaneously with EDMA now.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Jacob,

Regarding your channel setting, first of all, if you use two channel for example SAI_RX_DATA[1:0], you should set the RCM bit as 2b'11.

With the follwoing code:

base->RCR3 &= ~I2S_RCR3_RCE_MASK;

base->RCR3 |= I2S_RCR3_RCE(1U << format->channel);

the SDK set up the receiver channels. The first line clear RCM bits so that the second line can set the bits. But the second line: base->RCR3 |= I2S_RCR3_RCE(1U << format->channel); can set up one channel instead of two, i think it is a bug of the sai driver.

If you use two channel of SAI receiver, as you did, you can modify the code as:

base->RCR3 &= ~I2S_RCR3_RCE_MASK;

//base->RCR3 |= I2S_RCR3_RCE(1U << format->channel);

base->RCR3 |= I2S_RCR3_RCE_MASK;

For transmitter, it is the same.

Hope it can help you.

BR

XiangJun Rong

void SAI_RxSetFormat(I2S_Type *base,

sai_transfer_format_t *format,

uint32_t mclkSourceClockHz,

uint32_t bclkSourceClockHz)

{

uint32_t bclk = format->sampleRate_Hz * 32U * 2U;

/* Compute the mclk */

#if defined(FSL_FEATURE_SAI_HAS_MCLKDIV_REGISTER) && (FSL_FEATURE_SAI_HAS_MCLKDIV_REGISTER)

/* Check if master clock divider enabled */

if (base->MCR & I2S_MCR_MOE_MASK)

{

SAI_SetMasterClockDivider(base, format->masterClockHz, mclkSourceClockHz);

}

#endif /* FSL_FEATURE_SAI_HAS_MCLKDIV_REGISTER */

/* Set bclk if needed */

if (base->RCR2 & I2S_RCR2_BCD_MASK)

{

base->RCR2 &= ~I2S_RCR2_DIV_MASK;

base->RCR2 |= I2S_RCR2_DIV((bclkSourceClockHz / bclk) / 2U - 1U);

}

/* Set bitWidth */

if (format->protocol == kSAI_BusRightJustified)

{

base->RCR5 = I2S_RCR5_WNW(31U) | I2S_RCR5_W0W(31U) | I2S_RCR5_FBT(31U);

}

else

{

base->RCR5 = I2S_RCR5_WNW(31U) | I2S_RCR5_W0W(31U) | I2S_RCR5_FBT(format->bitWidth - 1);

}

/* Set mono or stereo */

base->RMR = (uint32_t)format->stereo;

/* Set data channel */

base->RCR3 &= ~I2S_RCR3_RCE_MASK;

base->RCR3 |= I2S_RCR3_RCE(1U << format->channel);

#if defined(FSL_FEATURE_SAI_FIFO_COUNT) && (FSL_FEATURE_SAI_FIFO_COUNT > 1)

/* Set watermark */

base->RCR1 = format->watermark;

#endif /* FSL_FEATURE_SAI_FIFO_COUNT */

}