- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for MCU

- :

- K60 Interrupt Priority

K60 Interrupt Priority

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

I have K60 Tower board: MK60FN1M0VLQ12.

In the reference manual, 3.2.2.1 Interrupt priority levels, and table Table 3-5. Interrupt vector assignments show the registers for each interrput. For example:

0x0000_013C 79 63 1 15 FTM1 Single interrupt vector for all sources

If I want to set the interrupt with PRIORITY 1:

I shall use register NVICIPR15, and

NVICIPR15 = 0x01;

Is this correct?

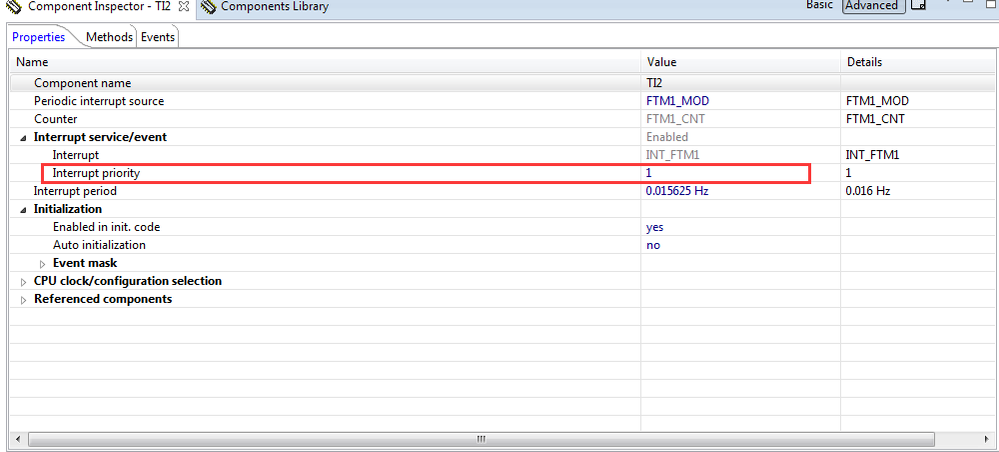

But the code generated by PE wizard:

//Enable Interrupt

NVICIP63 = NVIC_IP_PRI63(0x80);

/* NVICISER1: SETENA|=0x80000000 */

NVICISER1 |= NVIC_ISER_SETENA(0x80000000);

FTM1_SC |= FTM_SC_TOIE_MASK;

_int_install_isr(LDD_ivIndex_INT_FTM1, FC1_OnOverflow, NULL );

Why use NVICIP63 = NVIC_IP_PRI63(0x80); ?

what means to 0x80?

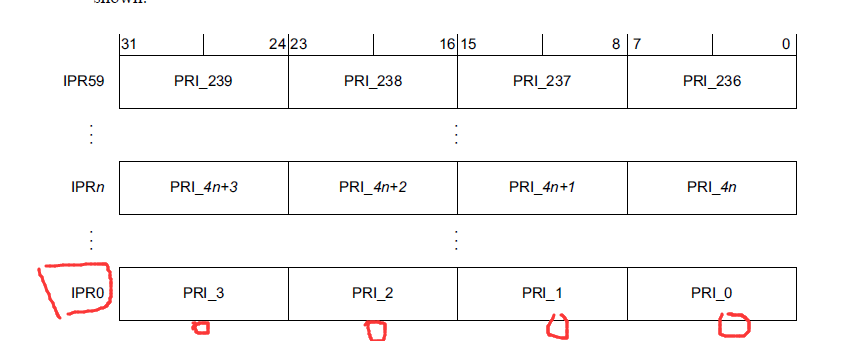

IPR registers contains 4 bits as stated in the section 3.2.2.1 Interrupt priority levels.

I am a little confused. What are priority levels (0-15 with 0 as highest priority?) or priorities from 0 - 0xFF ?

Thank you

David Zhou

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello David,

- Which version of IDE do you used ? I used the CW 10.6.4, when i set the FTM1 priority to

"1" , the generated code is :

/* NVICIP63: PRI63=0x10 */

NVICIP63 = NVIC_IP_PRI63(0x10);

The result is right .

- For this device , one byte(8 bit) support one interrupt priority use the NVIC_IPR register ,

while the low 4 bits have no effect, the default data is "0000" , so only the high 4 bits indicate

the priority . For example , if the priority is "1", the data should be 0x10, not 0x01 .

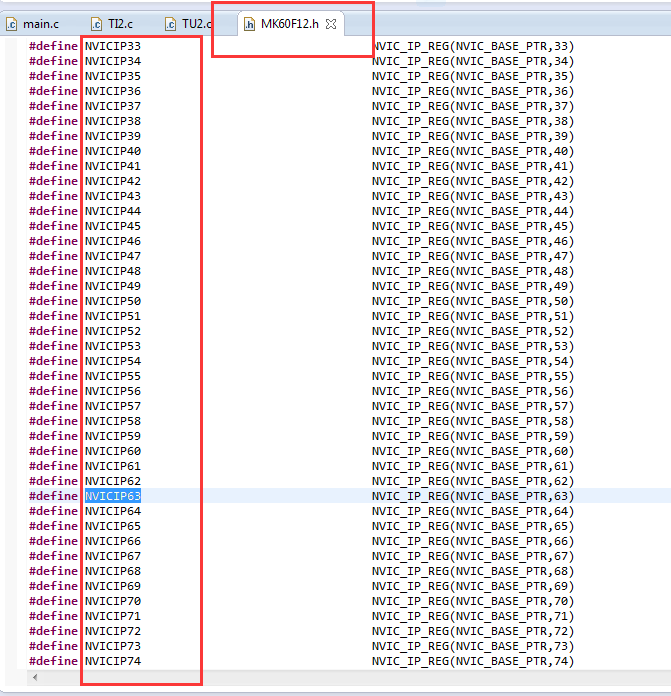

- About "NVICIPR15" , this is the define register on ARM M4 core, while , in this chip ,

it doesn't defined as this name . As we know , on NVICIPR register includes 4 bytes ,

in this chip , defined all the bytes :

From the RM of K60, we can see FTM1 IRQ is 63, so the result is NVICIP63 = NVIC_IP_PRI63(0x10);

Does this can helps you ?

Have a great day,

Alice

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello David,

- Which version of IDE do you used ? I used the CW 10.6.4, when i set the FTM1 priority to

"1" , the generated code is :

/* NVICIP63: PRI63=0x10 */

NVICIP63 = NVIC_IP_PRI63(0x10);

The result is right .

- For this device , one byte(8 bit) support one interrupt priority use the NVIC_IPR register ,

while the low 4 bits have no effect, the default data is "0000" , so only the high 4 bits indicate

the priority . For example , if the priority is "1", the data should be 0x10, not 0x01 .

- About "NVICIPR15" , this is the define register on ARM M4 core, while , in this chip ,

it doesn't defined as this name . As we know , on NVICIPR register includes 4 bytes ,

in this chip , defined all the bytes :

From the RM of K60, we can see FTM1 IRQ is 63, so the result is NVICIP63 = NVIC_IP_PRI63(0x10);

Does this can helps you ?

Have a great day,

Alice

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alice,

Thank you. That helps.

David Zhou