- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Configuring MIPI sensor

Configuring MIPI sensor

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Configuring MIPI sensor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I want to configure my scm qwks board to capture video from a ADV7281 Analog Devices dev board. I know I need to configure the imx6 to recognize this device. I am not sure where to start modifying the device trees for a mipi sensor. I have gone through many threads and the following debug checklist document.

https://community.nxp.com/docs/DOC-94312

First step is to check that GPIO/IOMUX settings are correct. What document must I reference to set these settings accordingly?

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ali

iomux settings means IOMUXC_GPR1[MIPI_IPU_MUX]

also one can look at

https://ez.analog.com/thread/50046

https://community.nxp.com/message/314760#comment-314760

kernel mainline the driver already supports ADV7181 MIPI interface:

http://lxr.free-electrons.com/source/drivers/media/i2c/adv7180.c

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

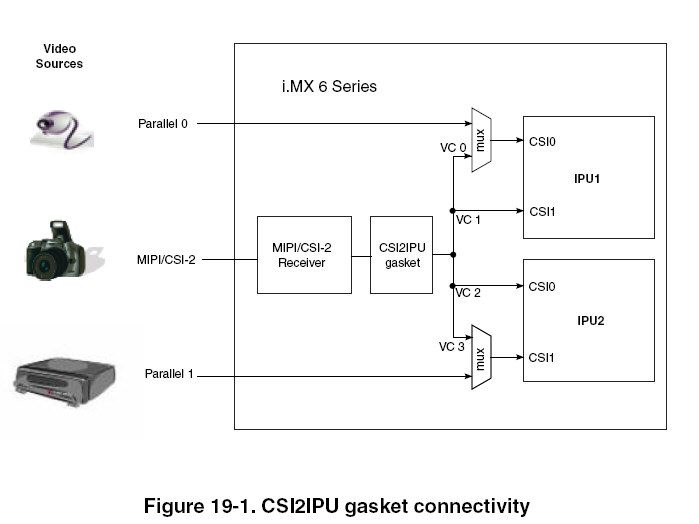

So I am at a point where I think I have everything configured. I am trying to configure VC2 to CSI0 in IPU2.

In imx6dql.dtsi the mipi/csi interface is defined.

mipi_csi: mipi_csi@021dc000 { /* MIPI-CSI */

compatible = "fsl,imx6q-mipi-csi2";

reg = <0x021dc000 0x4000>;

interrupts = <0 100 0x04>, <0 101 0x04>;

clocks = <&clks IMX6QDL_CLK_HSI_TX>,

<&clks IMX6QDL_CLK_EMI_SEL>,

<&clks IMX6QDL_CLK_VIDEO_27M>;

clock-names = "dphy_clk", "pixel_clk", "cfg_clk";

status = "disable";

};

In imx6dqscm_qwks_rev2.dts the mipi/csi is configured with IPU2(ipu_id = 1), CSI0(csi_id = 0), VC2 (v_channel=2) and 1 lane.

&mipi_csi {

status = "okay";

ipu_id = <1>;

csi_id = <0>;

v_channel = <2>;

lanes = <1>;

};

IPU2 is also defined and configured already in imx6qdl.dtsi. My issue is that when I read memory address 0x021dc004 (MIPI_CSI_N_LANES) I get 0x00000003, which means there are 4 active data lanes. After looking at the rest of the registers, everything is in reset. Any hints on why everything is in reset and/or what I have to configure to get it out of reset?