- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- i.MX257: Drive GPIO output low in Keeper enabled

i.MX257: Drive GPIO output low in Keeper enabled

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX257: Drive GPIO output low in Keeper enabled

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Champs,

A GPIO is connected to a FPGA and the GPIO set to Output High when running.

When S/W reset, they would like to drive the GPIO Low in order to reset the FPGA.

However the GPIO wouldn't go Low when reset.

They pulldown the pad externally in 10K resistor and set Keeper enabled during reset to IOMUX setting done.

(Keeper is disabled on normal operation).

Their question is,

With internal Keeper enabled, how much current should I give in order to driver the pin low?

I don't understand the question well but I think internal Keeper load doesn't effect on the current to drive the pin.

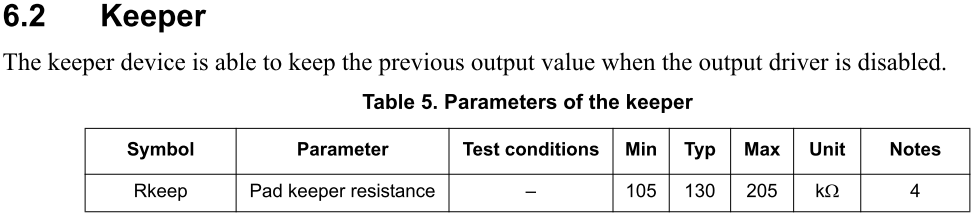

However from AN5078 "Influence of Pin Setting.." document describes Keeper has Typ 130K load.

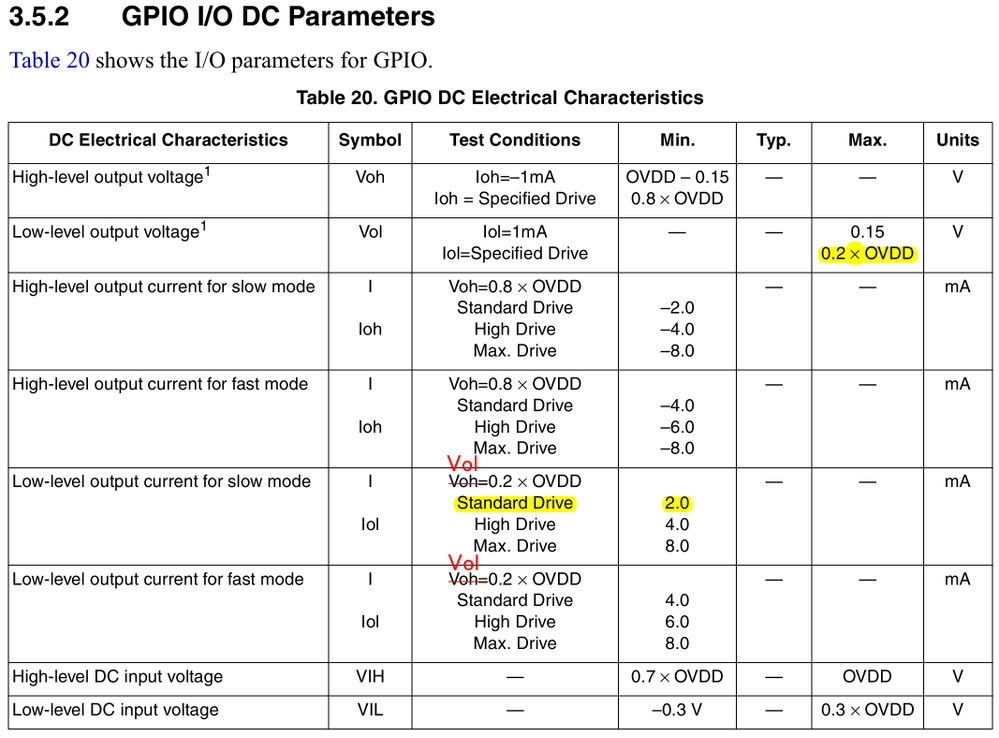

From i.MX25 datasheet, Iol is 2.0mA for slow mode and Standard Drive GPIO pins.

So in order to drive the pin Low, minimum 2.0mA can be input to i.MX25.

Regardless the load of external pullup/down resistors and FPGA loads, how much current they should give in order to drive the pin output low?

BR,

N.Shinozaki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unfortunately, I don't understand the question exactly. When the pin is configured as GPIO input with keeper disabled (default state of most pins out of reset), it behaves as hi-Z, so, any pulldown resistor (even 1MOhm) can keep it Low. When the pin is configured as GPIO input with keeper enabled, it behaves as equivalent resistance of typ. 130kOhm as you listed, connected to the current state level. In this case, 10kOhm pulldown should be enoug to always pull the pin over to Low state. If the pin is configured as GPIO output, trying to drive it externally to pull it over to another state is not a good pratice that can lead to permanent GPIO driver damage.

Have a great day,

Artur

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Artur,

Without considering Keeper impedance, do I just need to refer to IoL in the table 20?

For example, in "slow mode" and "Standard Drive", the GPIO can pull in Min. 2.0mA for VoL.

If we drive 2.1mA, the pin goes above VoL?

BR,

N.S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Nori Shinozaki,

Sorry for the delay, I was on the vacation.

Q. Without considering Keeper impedance, do I just need to refer to IoL in the table 20?

A. Yes, you are right.

Q. For example, in "slow mode" and "Standard Drive", the GPIO can pull in Min. 2.0mA for VoL.

If we drive 2.1mA, the pin goes above VoL?

A. Typically no, but it is not guaranteed to drive more than 2.0mA for these conditions.

Best Regards,

Artur

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Artur,

Thanks for comment.

>If the pin is configured as GPIO output, trying to drive it externally to pull it over to another state is not a good practice that can lead to permanent GPIO driver damage.

Please consider a case in which i.MX25 GPIO resets a FPGA.

When SW reset, i.MX25 GPIO needs to pull it down to produce active-low signal in order to reset the FPGA.

Isn't this recommended?

They have this design working with Renesus SoC.

BR,

Nori Shinozaki