- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5674F PLL Jitter on D_CLKOUT

MPC5674F PLL Jitter on D_CLKOUT

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

A have a customer who is using an MPC5674F at 264MHz. They drive EXTAL with a 12MHz hybrid oscillator so the input source is stable.

On the D_CLKOUT pin, they are seeing more than a little jitter coming out of the PLL. They haven’t spent time trying to understand the ins and outs of jitter measurements to quantify exactly how much jitter there is. There’s nothing visible for jitter on the 12MHz clock input, perhaps 1-2 percent on the D_CLKOUT pin.

They are concerned since the D_CLKOUT becomes the reference clock for a PLL in an external FPGA most likely exacerbating that PLL’s jitter.

They’re going back into layout soon and would like a recommendation of what can be done to minimize the 5674 PLL’s jitter. They have an LC filter on the VDDSYN input and are planning to get the components as close as possible to

the pin.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

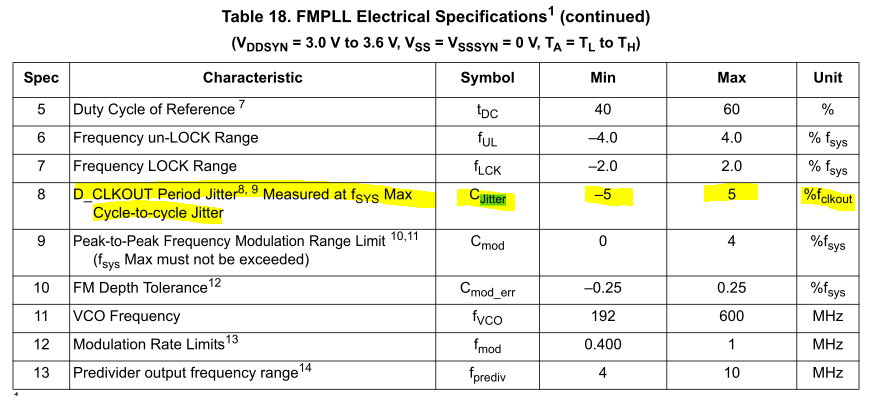

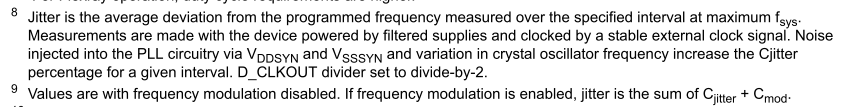

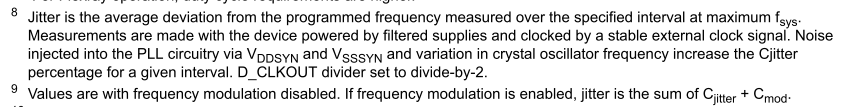

max jitter is specified as +/-5% of CLKOUT frequency, so 1-2% is still within limit.

Yes, to keep the jitter as low as possible, it is necessary to use stable external clock, filter supply voltage enough (especially VDDSYN) and follow general PCB design rules...

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

max jitter is specified as +/-5% of CLKOUT frequency, so 1-2% is still within limit.

Yes, to keep the jitter as low as possible, it is necessary to use stable external clock, filter supply voltage enough (especially VDDSYN) and follow general PCB design rules...

Regards,

Lukas