- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC4357 I2C Clock Rate

LPC4357 I2C Clock Rate

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC4357 I2C Clock Rate

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

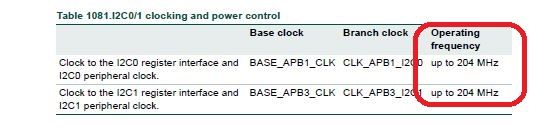

The I2C1 peripheral is clocked by CLK_APB3_I2C1. I initially had APB3_CLK, which is the base clock of CLK_APB3_I2C1, set to take as input PLL1, which is running at 204 MHz. Therefore I2C1 was clocked at 204 MHz.

When clocked at 204 MHz, the I2C1 peripheral runs for about a minute and then starts to fail. It either will not generate any more interrupts or it will generate continuous interrupts with state=0, which indicates an I2C bus error.

If I change APB3_CLK to run from IDIVA, which is set to divide PLL1 by 2, I2C1 runs fine. I checked the errata and there's no mention of I2C1 having issues at 204 MHz. The 4358 UM (UM10503) explicitly states:

Clock to the I2C1 register interface and I2C1 peripheral clock: BASE_APB3_CLK CLK_APB3_I2C1 up to 204 MHz

Anyone know why I2C1 won't run at 204 MHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

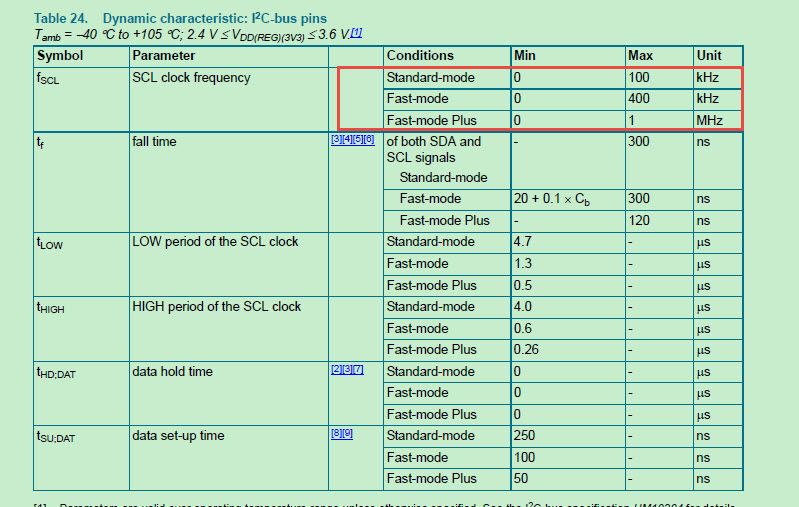

The I2C SCK frequency I was using was 100 kHz. That's well within the maximum frequency supported by the I2C peripheral on the LPC4357.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jerry Gardner,

Sorry for my later reply!

After checking with our LPC AE, I get that the LPC4357 can work with 208Mhz, and the hardware have no bug, so it may relates to your I2C code.

Did you try to use our LPCopen library to test it?

You can find the LPC4357 lpcopen code from this URL:

LPCOpen Software for LPC43XX|NXP

After you use the LPCopen I2C code, if you still have problem, please tell me!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jerry,

Did you check your I2C SCL clock frequency?

From the datasheet,

You can get that the max scl clock frequency is 1Mhz, so you should make sure when you use the clock for the I2C module, you should keep the I2C SCK clock frequency in the range defined by the datasheet.

Please check it on your side.

If you still have question, please kindly let me know!

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm not talking about the I2C data rate, I'm taking about the peripheral clock used to clock the I2C peripheral. The user's manual says that it can be clocked at up to 204 MHz, which is what I initially tried. The peripheral was unstable at this clock rate, but is rock solid at 102 MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jerry,

Thank you for your more details.

I just want to know, when you use 204Mhz clock as the clock source of I2C peripheral, what the data rate you are configuring? Whether it is exceed the highest SCK clock freqency?

Did you test the I2C line wave when use 204Mhz?

Have a great day,

Jingjing

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------