- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for MCU

- :

- Paged memory for MC9S08AC128

Paged memory for MC9S08AC128

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a PRM file for MC9S08AC128 for which I am not using Paged Memory Concept.I would like to know whether the memory allocation will be fine for data and code .Also I have only a single pragma statement # pragma DATA_SEG MySeg for some of the gloval variables in a single .c file and for rest it is # pragma DATA_SEG Default in the same file .Whether it is required to use the Paged memory concept .Also in the map file generated ,only few of the variables use the PPAGE_2 ,rest use ROM,PAGE0,ROM1.

SEGMENTS /* Here all RAM/ROM areas of the device are listed. Used in PLACEMENT below. */

MY_STK = NO_INIT 0x15FF TO 0x17FF;

RAM1 = READ_WRITE 0x0080 TO 0x01FF;

RAMSEG = READ_WRITE 0x0200 TO 0x0370;

RAM2 = READ_WRITE 0x0372 TO 0x15FE;

RAM3 = READ_WRITE 0x1870 TO 0x20EF;

ROM = READ_ONLY 0x20F0 TO 0x7FFF;

ROM1 = READ_ONLY 0xC000 TO 0xFF9B;

/* banked FLASH ROM */

PPAGE_0 = READ_ONLY 0x008000 TO 0x00A0EF; /* PAGE partially contained in ROM segment */

PPAGE_2 = READ_ONLY 0x028000 TO 0x02BFFF;

PPAGE_4 = READ_ONLY 0x048000 TO 0x04BFFF;

PPAGE_5 = READ_ONLY 0x058000 TO 0x05BFFF;

PPAGE_6 = READ_ONLY 0x068000 TO 0x06BFFF;

PPAGE_7 = READ_ONLY 0x078000 TO 0x07BFFF;

END

PLACEMENT /* Here all predefined and user segments are placed into the SEGMENTS defined above. */

MySeg INTO RAM1;

DEFAULT_RAM INTO RAM2,RAM3;

DEFAULT_ROM, ROM_VAR, STRINGS INTO ROM,PPAGE_0,ROM1,PPAGE_2,PPAGE_4,PPAGE_5,PPAGE_6,PPAGE_7; /* See compiler option -OnB=b. */

//PAGED_ROM INTO PPAGE_0,ROM1,PPAGE_2,PPAGE_4,PPAGE_5,PPAGE_6,PPAGE_7;

SSTACK INTO MY_STK;

END

STACKSIZE 0x200

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

if the non-paged memory size is enough for your code, you needn't use paged memory. otherwise, it's necessary to use paged memory.

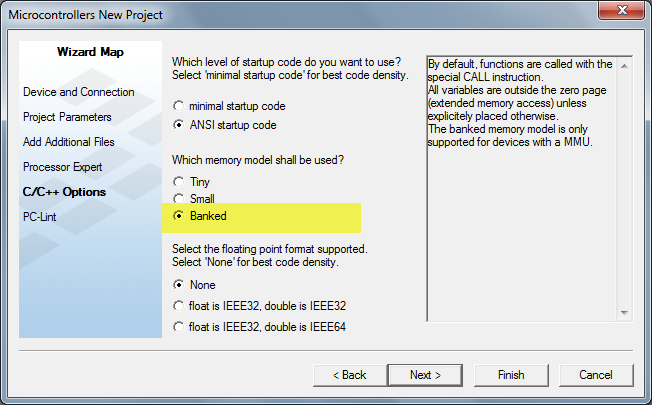

when use paged memory, we need choose banked memory model:

we have an3730, an3730sw covered this topic. see:

http://cache.nxp.com/files/microcontrollers/doc/app_note/AN3730.pdf?fsrch=1&sr=2&pageNum=1

can this help you?

Have a great day,

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

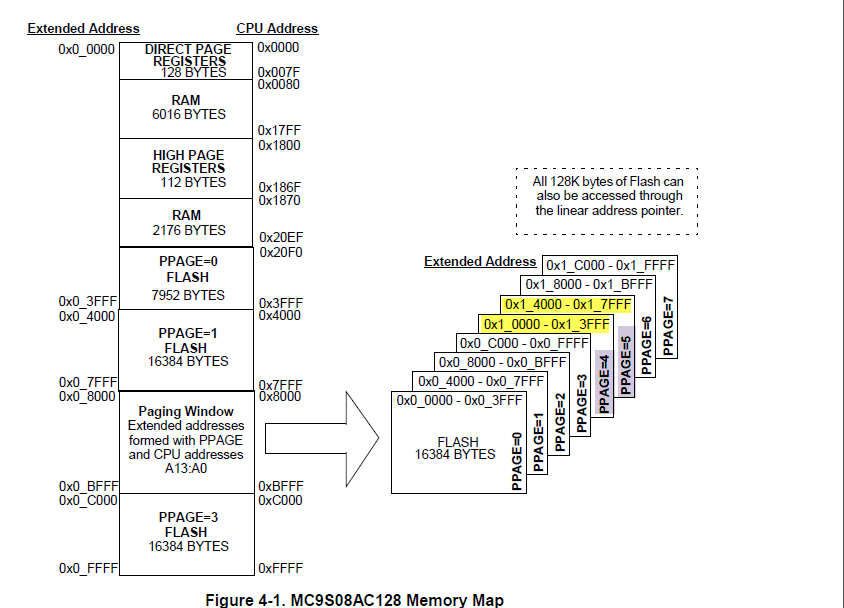

according to memory map, 0x10000 to 0x17fff is linear address for page4 and page5.

when use linear address mode, this range of memory address is 0x10000 to 0x17fff; if use page memory mode, the same memory is (0x048000 TO 0x04BFFF, and 0x058000 TO 0x05BFFF); user must choose one mode of them.

in banked memory mode, paged memory can be used for allocating code. code(function ) is inherently accessed by __far. you needn't use #pragma for it.

however from what i am understanding linear address is only for data access. so you can't define all of the flash memory in linear address mode in prm file. code(function) must use paged and non-paged memory. data access can use linear address. see two demo code in an3730

Have a great day,

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang,

Whether the memory range 0x10000 to 0x17fff is part of Paged memory and to use this I have to use banked memory model or can use small memory model with MMU ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang,

For the above PRM file, memory range 0x10000 to 0x17fff is not mentioned ,Whether we can use part of paged memory model or as part of small memory model

Since for the calcualtion of CRC ,While reading s-record data for 0x10000 to 0x17fff ,it is nto able to calcualte CRC

So for the above PRM ,whetehr I can modify as following for the Flash memory and I need small meory after 0xffff

ROM = READ_ONLY 0x20F0 TO 0x7FFF;

ROM1 = READ_ONLY 0xC000 TO 0xFF9B;

/* banked FLASH ROM */

PPAGE_0 = READ_ONLY 0x008000 TO 0x00A0EF; /* PAGE partially contained in ROM segment */

PPAGE_1 = READ_ONLY 0x10000 TO 0x17fff

and under SEGMENTS section

DEFAULT_ROM, ROM_VAR, STRINGS INTO ROM,PPAGE_0,ROM1,PPAGE_1;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

if the non-paged memory size is enough for your code, you needn't use paged memory. otherwise, it's necessary to use paged memory.

when use paged memory, we need choose banked memory model:

we have an3730, an3730sw covered this topic. see:

http://cache.nxp.com/files/microcontrollers/doc/app_note/AN3730.pdf?fsrch=1&sr=2&pageNum=1

can this help you?

Have a great day,

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhang,

For the above PRM file, memory range 0x10000 to 0x17fff is not mentioned ,Whether we can use part of paged memory model or as part of small memory model

Since for the calcualtion of CRC ,While reading s-record data for 0x10000 to 0x17fff ,it is nto able to calcualte CRC

So for the above PRM ,whetehr I can modify as following for the Flash memory and I need small meory after 0xffff

ROM = READ_ONLY 0x20F0 TO 0x7FFF;

ROM1 = READ_ONLY 0xC000 TO 0xFF9B;

/* banked FLASH ROM */

PPAGE_0 = READ_ONLY 0x008000 TO 0x00A0EF; /* PAGE partially contained in ROM segment */

PPAGE_1 = READ_ONLY 0x10000 TO 0x17fff

and under SEGMENTS section

DEFAULT_ROM, ROM_VAR, STRINGS INTO ROM,PPAGE_0,ROM1,PPAGE_1;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Jennie for that information

After usign the Banked memory ,software uses some of the section PPAGE2 from the PRM file given above,but

whether for those variables which are getting allocation in PPAGE2 I have to use # pragma statement for the memory to get allocated correctly. Also since those variables are getting allocated in PPAGE 2 ,in the above PRM File I have to move PPAGE2 to PAGED_ROM from DEFAULT_ROM and use pragma statement for PAGED_ROM.What exactly PAGED_ROM means

See the allocation in map file from PAGED_ROM

*********************************************************************************************

SECTION-ALLOCATION SECTION

Section Name Size Type From To Segment

---------------------------------------------------------------------------------------------

MySeg 301 R/W 0x80 0x1AC RAM1

.data 855 R/W 0x372 0x6C8 RAM2

.text 23594 R 0x2129 0x7D52 ROM

.rodata 9203 R 0xD884 0xFC76 ROM1

.rodata1 1 R 0xFC77 0xFC77 ROM1

.stack 512 N/I 0x15FF 0x17FE MY_STK

.abs_section_200 40 N/I 0x200 0x227 .absSeg77

.abs_section_228 40 N/I 0x228 0x24F .absSeg78

.abs_section_250 80 N/I 0x250 0x29F .absSeg2

.abs_section_2a0 80 N/I 0x2A0 0x2EF .absSeg3

.abs_section_2f0 128 N/I 0x2F0 0x36F .absSeg4

.abs_section_ffbd 1 R 0xFFBD 0xFFBD .absSeg5

.abs_section_ffbf 1 R 0xFFBF 0xFFBF .absSeg6

.abs_section_ffcc 150 R 0xFFCC 0x10061 .absSeg8

.abs_section_0 1 N/I 0x0 0x0 .absSeg9

.abs_section_1 1 N/I 0x1 0x1 .absSeg10

.abs_section_2 1 N/I 0x2 0x2 .absSeg11

.abs_section_3 1 N/I 0x3 0x3 .absSeg12

.abs_section_4 1 N/I 0x4 0x4 .absSeg13

.abs_section_5 1 N/I 0x5 0x5 .absSeg14

.abs_section_6 1 N/I 0x6 0x6 .absSeg15

.abs_section_7 1 N/I 0x7 0x7 .absSeg16

.abs_section_8 1 N/I 0x8 0x8 .absSeg17

.abs_section_9 1 N/I 0x9 0x9 .absSeg18

.abs_section_a 1 N/I 0xA 0xA .absSeg19

.abs_section_b 1 N/I 0xB 0xB .absSeg20

.abs_section_c 1 N/I 0xC 0xC .absSeg21

.abs_section_d 1 N/I 0xD 0xD .absSeg22

.abs_section_1c 1 N/I 0x1C 0x1C .absSeg23

.abs_section_20 1 N/I 0x20 0x20 .absSeg24

.abs_section_25 1 N/I 0x25 0x25 .absSeg25

.abs_section_28 1 N/I 0x28 0x28 .absSeg26

.abs_section_2b 1 N/I 0x2B 0x2B .absSeg27

.abs_section_3a 1 N/I 0x3A 0x3A .absSeg28

.abs_section_3b 1 N/I 0x3B 0x3B .absSeg29

.abs_section_3c 1 N/I 0x3C 0x3C .absSeg30

.abs_section_3d 1 N/I 0x3D 0x3D .absSeg31

.abs_section_3e 1 N/I 0x3E 0x3E .absSeg32

.abs_section_3f 1 N/I 0x3F 0x3F .absSeg33

.abs_section_48 1 N/I 0x48 0x48 .absSeg34

.abs_section_49 1 N/I 0x49 0x49 .absSeg35

.abs_section_4a 1 N/I 0x4A 0x4A .absSeg36

.abs_section_4b 1 N/I 0x4B 0x4B .absSeg37

.abs_section_50 1 N/I 0x50 0x50 .absSeg38

.abs_section_51 1 N/I 0x51 0x51 .absSeg39

.abs_section_52 1 N/I 0x52 0x52 .absSeg40

.abs_section_53 1 N/I 0x53 0x53 .absSeg41

.abs_section_55 1 N/I 0x55 0x55 .absSeg42

.abs_section_58 1 N/I 0x58 0x58 .absSeg43

.abs_section_59 1 N/I 0x59 0x59 .absSeg44

.abs_section_5a 1 N/I 0x5A 0x5A .absSeg45

.abs_section_5b 1 N/I 0x5B 0x5B .absSeg46

.abs_section_5c 1 N/I 0x5C 0x5C .absSeg47

.abs_section_1800 1 N/I 0x1800 0x1800 .absSeg48

.abs_section_1802 1 N/I 0x1802 0x1802 .absSeg49

.abs_section_1840 1 N/I 0x1840 0x1840 .absSeg50

.abs_section_1841 1 N/I 0x1841 0x1841 .absSeg51

.abs_section_1844 1 N/I 0x1844 0x1844 .absSeg52

.abs_section_1845 1 N/I 0x1845 0x1845 .absSeg53

.abs_section_1848 1 N/I 0x1848 0x1848 .absSeg54

.abs_section_1849 1 N/I 0x1849 0x1849 .absSeg55

.abs_section_184c 1 N/I 0x184C 0x184C .absSeg56

.abs_section_184d 1 N/I 0x184D 0x184D .absSeg57

.abs_section_1850 1 N/I 0x1850 0x1850 .absSeg58

.abs_section_1851 1 N/I 0x1851 0x1851 .absSeg59

.abs_section_1854 1 N/I 0x1854 0x1854 .absSeg60

.abs_section_1855 1 N/I 0x1855 0x1855 .absSeg61

.abs_section_1858 1 N/I 0x1858 0x1858 .absSeg62

.abs_section_1859 1 N/I 0x1859 0x1859 .absSeg63

.abs_section_21 2 N/I 0x21 0x22 .absSeg64

.abs_section_22 2 N/I 0x22 0x23 .absSeg65

.abs_section_23 2 N/I 0x23 0x24 .absSeg66

.abs_section_24 2 N/I 0x24 0x25 .absSeg67

.abs_section_26 2 N/I 0x26 0x27 .absSeg68

.abs_section_27 2 N/I 0x27 0x28 .absSeg69

.abs_section_29 2 N/I 0x29 0x2A .absSeg70

.abs_section_2a 2 N/I 0x2A 0x2B .absSeg71

.abs_section_2c 2 N/I 0x2C 0x2D .absSeg72

.abs_section_2d 2 N/I 0x2D 0x2E .absSeg73

.abs_section_38 1 N/I 0x38 0x38 .absSeg74

.abs_section_39 1 N/I 0x39 0x39 .absSeg75

.abs_section_371 1 N/I 0x371 0x371 .absSeg76

.abs_section_2bfc4 8 N/I 0x2BFC4 0x2BFCB .absSeg79

.abs_section_370 1 N/I 0x370 0x370 .absSeg80

.abs_section_2bfc0 4 N/I 0x2BFC0 0x2BFC3 .absSeg81

.bss 357 R/W 0x6C9 0x82D RAM2

.startData 38 R 0x2103 0x2128 ROM

.init 19 R 0x20F0 0x2102 ROM

.common 1382 R/W 0x82E 0xD93 RAM2

NON_BANKED 784 R 0xFC78 0xFF87 ROM1

.copy 868 R 0x280BA 0x2841D PPAGE_2

PPAGE_0_82 16127 R 0x8000 0xBEFE PPAGE_0

ROM1_83 6276 R 0xC000 0xD883 ROM1

PPAGE_2_84 186 R 0x28000 0x280B9 PPAGE_2

Summary of section sizes per section type:

READ_ONLY (R): DFA0 (dec: 57248)

READ_WRITE (R/W): B4F (dec: 2895)

NO_INIT (N/I): 3CB (dec: 971)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

If you use banked memory model,

code(function ) is inherently accessed by __far. you needn't use #pragma for it.

while data is accessed by __near. thus you need use #pragma to define variable in paged memory.

Have a great day,

Jennie Zhang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------