- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC1778 SWD SWCLK Pull Up or Pull Down

LPC1778 SWD SWCLK Pull Up or Pull Down

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC1778 SWD SWCLK Pull Up or Pull Down

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi we are about to make revised PCB for our custom 1778 board to fix errors/problems.

However, before the lasted PCB is finalised, I have noticed a contradiction in the requirements

for the SWD SWCLK signal.

In this FAQ "Design Considerations for Debug" at http://www.lpcware.com/content/faq/lpcxpresso/debug-design

it shows a pull DOWN on the clock line.

JTAG Mode SWD Mode Signal Notes TCK SWCLK Clock into the core Use 10K-100K Ohm pull-down resistor to GND |

In the latest UM10470 for LPC178x/7x Fig 176 "Cortex Debug Connector" it shows a pull UP

[Also in UM10503]

The schematic for the e.g the MCB1700 board uses a pull down.

Our board in revisions A and B use a pull down and debug certainly works with the original LPC-Link

and with LPC-Link2 (Redlink)

So what is the OFFICIAL requirements.

Is it the user manual(s) or the FAQ in error?

And does it really matter after all is said and done?

Regards Mike

NXP: If you could answer promptly, as we need to get these PCB's made soonest.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unlike Mike, I'm using a device which shares its serial wire pins with GPIO. If the pull-up is enabled in IOCON as its default condition out of reset, doesn't it have a pull-up? Could you please clarify.

If I were to add a pull-down on SWCLK, and just happened to use a value which sinks the same amount of current that the internal pull-up sources, then it will be biassed right in the middle - just where it is most vulnerable to noise, and just where it will make the following stage draw current from the supply.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unlike Mike, I'm using a device which shares its serial wire pins with GPIO. If the pull-up is enabled in IOCON as its default condition out of reset, doesn't it have a pull-up? Could you please clarify.

This message is a bit old but I will reply it as it might help other people and I asked myself the same question tonight. Here is the answer from Design Considerations for Debug :

Some MCUs do not include internal pull-up or pull-down resistors on JTAG/SWD pins. You will need to review the datasheet for the specific MCU being used to confirm. Where internal resistors are not provided, these should be added externally onto your board as detailed above. You may use resistors between 10K and 100K for these signals. This will prevent the signals from floating when they are not connected to anything. Failure to do this will lead to, at best, unreliable debug connections, or more likely no ability to debug at all.

If an internal resistor is provided for a pin by the MCU, then an external resistor is not required for that pin. But if external resistor is provided in such cases, then it must match that provided internally by the MCU.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hmm, actually NXP Documentation does not agree with above NXP statement: "But if external resistor is provided in such cases, then it must match that provided internally by the MCU."

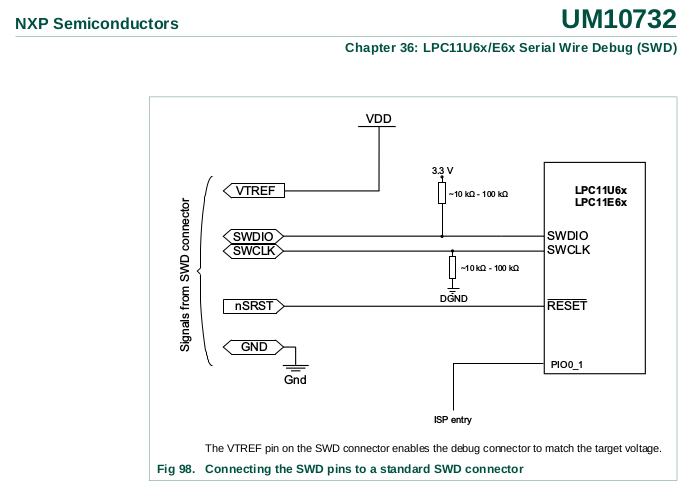

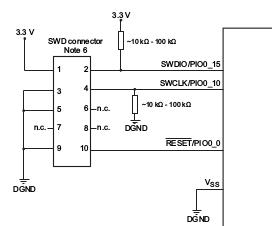

In the LPC11U6x User Manual and Data sheet it is said SWDIO and SWCLK have an internal pull-up for SWDIO and pull-down for SWCLK by default. But both documents contain a diagram that shows the recommendation to add a pull-up and pull-down resistors. And the value of these resistors do not necessary match the internal MCU...

So what should be done for LPC11U6x?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the clarification.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For SWCLK, a pull-down is recommended, although you can alternatively use a pull-up. The main thing is that it does not float.

[We've added a note to the Design Considerations for Debug FAQ for this, and will pass on the request for this to be made clearer in future MCU user manuals.]

@IanB - I would also like to emphasis that not putting the recommended pull-ups/pull-downs on the debug lines is at best likely to lead to unreliable debug connections.

Regards,

LPCXpresso Support

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quote: NXP_Paul

Mike

I think that this pin should have a pull-down since this is what I see on all the demo boards, and your board works with this configuration as well.

I will try to confirm this, but I probably can't get you an answer today.

Paul

Hi Paul, did you manage to confirm this?

Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Fair enough - and when NXP answers your question, perhaps they'd like to comment on the pull-up pull-down conflict for the LPC11xx devices.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The LPC1778 however has dedicated JTAG/SWD lines.

The user manual states internal pullups for !TRST, TDI and TMS (SWIO) but nothing for TDO or TCK (SWCLK).

So my question stands.

Mike.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have used several LPC devices, and have not used pull-ups or pull-downs on the SWD lines.

If you look at the relevant section in IOCON the pins both start up with a pull-up enabled. The pull-ups on these devices are specified between 15µA and 85µA, so are equivalent to having a pull-up resistor between 39k and 220k. It seems a bit daft to add a pull-down resistor - it's a recipe to set the input voltage at some intermediate value where it is more vulnerable to noise, and if it is like any other CMOS gate, cause the input devices to draw current from the supply.

SWCLK is a single direction signal, so is always driven from the programmer.

SWDIO is bidirectional, and if you watch it on a 'scope you can see that it slowly floats upwards in the gaps when it is driven by neither end.

One thing did flummox me for a while. On a LPC12xx, when the power to the board is removed, there will be voltage on Vdd that is supplied through the SWCLK/SWDIO pins, but on an LCP11xx there isn't. I eventually realised why - the LPC11xx has 5V tolerant inputs, and the LPC12xx doesn't. That means the LPC12xx has diodes between inputs and Vdd, and the LPC11xx doesn't. The LPC12xx gets supplied from SWCLK/SWDIO through its protection diodes.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for that.

I have a few days grace [management level red-tape for the accountants].

I was wondering:

Does it matter which way the pin is tied (as long as it is one or the other) because any

adapter will be actively driving the pin, and if no adapter is fitted the line will not be floating.

I seem to remember that a hardware engineer once told me that a pull down on an

unused input is better in that there is a lower leakage current (whatever that might be).

So really (if the above is valid) the question is why the difference between the FAQ and the UM(s).

Still, it will be good to have a definitive ruling form the actual silicon implementers.

Regards, Mike

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Mike

I think that this pin should have a pull-down since this is what I see on all the demo boards, and your board works with this configuration as well.

I will try to confirm this, but I probably can't get you an answer today.

Paul