- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Ethernet controller CANNOT receive the data well. For MPC6748G

Ethernet controller CANNOT receive the data well. For MPC6748G

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Ethernet controller CANNOT receive the data well. For MPC6748G

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear All,

When we used the Ethernet driver demo code got from NXP supporter, we found that the received data is wrong.

Could some help us?

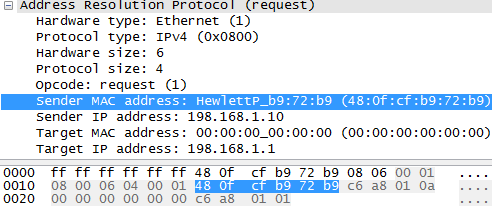

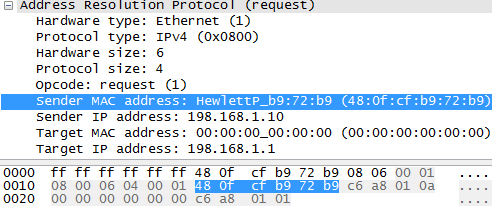

The sent data from PC is that:

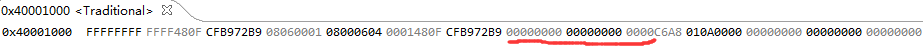

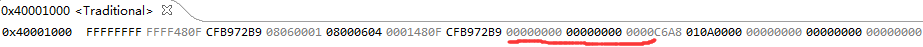

However, we don't know why the received data have 10 Bytes 0x00 in the middle of the data. And lot some data such as the end four data(C6 A8 01 01).

The data buffer defined as below:

/* Buffer descriptors: */

__attribute__(( aligned(64) ))

volatile u32_t au32RxBDs[8]; /* Each BD is 32 bytes */

__attribute__(( aligned(64) ))

volatile u32_t au32TxBDs[8];

/* Buffers: */

__attribute__(( aligned(64) ))

u8_t au8RxBuffs[RX_BUFF_SIZE];

__attribute__(( aligned(64) ))

u8_t au8TxBuff[TX_BUF_SIZE]; /* We will use only one data buffer for transmissions from all

buffer descriptors */

the Init function is below:

void Eth_Init(void)

{

volatile u8_t u8i;

Reg32Write(ENET_ECR, 0x00000001U); /* Reset controller */

/* Wait until the reset is finished */

for(u8i = 0U; u8i < 30U; u8i++)

{

; /* Intentionally empty loop - just delay the execution */

}

Reg32Write(ENET_EIMR, 0U); /* Disable all interrupts */

Reg32Write(ENET_EIR, 0xffffffffU); /* Clear all interrupt flags*/

Reg32Write(ENET_RDSR, (u32_t)au32RxBDs); /* RX BD ring start */

Reg32Write(ENET_TDSR, (u32_t)au32TxBDs); /* TX BD ring start */

Reg32Write(ENET_MSCR, 14U);

Reg32Write(ENET_PALR, 0x11223344U); /* MAC address */

Reg32Write(ENET_PAUR, 0x55668808U);

Reg32Write(ENET_RCR, ((RX_BUFF_SIZE<<16U)| 0x4)); /* Configure receiver - loopback disabled */

Reg32Write(ENET_MRBR, RX_BUFF_SIZE); /* RX buffer size */

Reg32Write(ENET_TCR, 0x4U); /* Configure transmitter */

Reg32Write(ENET_MIBC, 0x0U); /* Configure transmitter */

Reg32Write(ENET_ECR, 0x00000012U); /* Enhanced descriptors, enable controller */

au32RxBDs[0U] = 0x80000000U; /* Set the Empty bit, the rest is written by HW */

au32RxBDs[1U] = (u32_t)au8RxBuffs; /* Data pointer */

au32RxBDs[2U] = 0x00800000U; /* Set the EIR[RXF] when frame received */

au32RxBDs[3U] = 0U;

au32RxBDs[4U] = 0U;

au32RxBDs[5U] = 0U;

au32RxBDs[6U] = 0U;

au32RxBDs[7U] = 0U;

/* Remember buffer position which has been read by SW as the last one */

au32RxBDs[0] = 0xA0000000; /* Set the Empty bit and the Wrap bit */

/* Tx */

au32TxBDs[0U] = 0x00000000U; /* Clear the Ready bit, the rest will be set later */

au32TxBDs[1U] = (u32_t)au8TxBuff; /* Data pointer */

au32TxBDs[2U] = 0x00000000U; /* No interrupt needed */

au32TxBDs[3U] = 0U;

au32TxBDs[4U] = 0U;

au32TxBDs[5U] = 0U;

au32TxBDs[6U] = 0U;

au32TxBDs[7U] = 0U;

au32TxBDs[0] = 0x20000000; /* Set the Empty bit and the Wrap bit */

/* Remember position of the buffer to be transmitted as the next one */

/* Inform the controller tha some new receive buffers are available, note that

after this step the first one data pointer changes are ignored by the controller

and the original value is written into the descriptor after the buffer is filled

in with the received frame data. */

Reg32Write(ENET_RDAR, 0xFFFFFFFFU);

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

could you please share your project?

What tool do you use for frame generating from PC? Do you use directly wireshark, or you have some plugin?

Regards,

Martin