- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- T-Series

- :

- Not able to fuse NOR flash using DDR3 in T1040

Not able to fuse NOR flash using DDR3 in T1040

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Not able to fuse NOR flash using DDR3 in T1040

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

In my custom board, which is based on T1040 RDB, i have DDR3 module MT4KTF25664Hz-1G6E1.(different from RDB board). I'm unable to load only Uboot file into NOR flash by using "T1040RDB_init_core.tcl". (fused RCW properly). I tried file called "T1040RDB_init_sram.tcl" and its working. what i understood is first file uses DDR values while second not.

pls clear me what are the main differences between these two files?? What all changes are required in file "T1040RDB_init_core.tcl" to work properly.

Looking for prompt reply...

--

regards,

Gourav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Init file looks fine, but I notice that you change the the Target RAM size from Flash Programmer Task from 0x00180000 to 0x00006130. Note that Address and Size from here are used by flash programmer algorithm when run.

Also, you can check from CW if your DDR is correctly initialize by using Memory view to check the DDR space or from Debugger Shell to read/write (mem <address>; mem <address> = value) from a specific DDR address.

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you add your init file?

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

# #######################################################################################

# Initialization file for T1040 RDB board

# Clock Configuration:

# CPU0: 1200/1400MHz, CCB: 600MHz,

# DDR: 800MHz (1600 MT/s data rate) (Asynchronous), IFC: 150MHz,

# FMAN1: 600MHz, QMAN: 300MHz, PME: 300MHz

# #######################################################################################

# Choose which core will initialize the board

variable master_core 0

variable ECC_EN 1

variable CCSRBAR 0xFE000000

proc CCSR_ADDR {reg_off} {

global CCSRBAR

return i:0x[format %x [expr {$CCSRBAR + $reg_off}]]

}

proc init_board {} {

# disable Boot Space Translation

mem [CCSR_ADDR 0x28] = 0x00000000

##################################################################################

# Local Access Windows Setup

# LAW0 to IFC (NOR) - 128M

mem [CCSR_ADDR 0xc00] = 0x00000000

mem [CCSR_ADDR 0xc04] = 0xE8000000

mem [CCSR_ADDR 0xc08] = 0x81F0001A

# LAW1 to IFC (CPLD) - 128K

mem [CCSR_ADDR 0xc10] = 0x00000000

mem [CCSR_ADDR 0xc14] = 0xFFDF0000

mem [CCSR_ADDR 0xc18] = 0x81F00010

# LAW2 to DCSR - 4M

mem [CCSR_ADDR 0xc20] = 0x00000000

mem [CCSR_ADDR 0xc24] = 0xF0000000

mem [CCSR_ADDR 0xc28] = 0x81D00015

# LAW3 to IFC (NAND) - 64K

mem [CCSR_ADDR 0xc30] = 0x00000000

mem [CCSR_ADDR 0xc34] = 0xFF800000

mem [CCSR_ADDR 0xc38] = 0x81F0000F

# LAW15 to DDR (Memory Complex 1) - 2G

mem [CCSR_ADDR 0xcf0] = 0x00000000

mem [CCSR_ADDR 0xcf4] = 0x00000000

mem [CCSR_ADDR 0xcf8] = 0x8100001E

##################################################################################

# DDR Controller Setup

# Get DDR type: 0 - DDR4; 1 - DDR3

# set DCFG_CCSR_PORSR2 [mem [CCSR_ADDR 0xE0004]]

# set DDR_TYPE [expr ($DCFG_CCSR_PORSR2 & 0x20000000) >> 29]

# DDR_SDRAM_CFG

mem [CCSR_ADDR 0x8110] = 0x47040000

# DDR_CS0_BNDS

mem [CCSR_ADDR 0x8000] = 0x7F

# DDR_CS1_BNDS

mem [CCSR_ADDR 0x8008] = 0x00000000

# DDR_CS0_CONFIG

mem [CCSR_ADDR 0x8080] = 0x80044302

# DDR_CS1_CONFIG

mem [CCSR_ADDR 0x8084] = 0x00000000

# DDR_CS0_CONFIG_2

mem [CCSR_ADDR 0x80c0] = 0x00000000

# DDR_CS1_CONFIG_2

mem [CCSR_ADDR 0x80c4] = 0x00000000

# DDR_TIMING_CFG_3

mem [CCSR_ADDR 0x8100] = 0x00060000

# DDR_TIMING_CFG_0

mem [CCSR_ADDR 0x8104] = 0x4011000c

# DDR_TIMING_CFG_1

mem [CCSR_ADDR 0x8108] = 0x6e6a0644

# DDR_TIMING_CFG_2

mem [CCSR_ADDR 0x810C] = 0x002880d0

# DDR_SDRAM_CFG_2

mem [CCSR_ADDR 0x8114] = 0x00401900

# DDR_SDRAM_MODE

mem [CCSR_ADDR 0x8118] = 0x00441420

# DDR_SDRAM_MODE_2

mem [CCSR_ADDR 0x811C] = 0x00800000

# DDR_SDRAM_MODE_3

mem [CCSR_ADDR 0x8200] = 0x00001420

# DDR_SDRAM_MODE_4

mem [CCSR_ADDR 0x8204] = 0x00800000

# DDR_SDRAM_MODE_5

mem [CCSR_ADDR 0x8208] = 0x000

# DDR_SDRAM_MODE_6

mem [CCSR_ADDR 0x820C] = 0x00000000

# DDR_SDRAM_MODE_7

mem [CCSR_ADDR 0x8210] = 0x00000

# DDR_SDRAM_MODE_8

mem [CCSR_ADDR 0x8214] = 0x00000000

# DDR_SDRAM_MD_CNTL

mem [CCSR_ADDR 0x8120] = 0x00000000

# DDR_SDRAM_INTERVAL

mem [CCSR_ADDR 0x8124] = 0x06180100

# DDR_DATA_INIT

mem [CCSR_ADDR 0x8128] = 0xdeadbeef

# DDR_SDRAM_CLK_CNTL

mem [CCSR_ADDR 0x8130] = 0x02000000

# DDR_INIT_ADDR

mem [CCSR_ADDR 0x8148] = 0x00000000

# DDR_INIT_EXT_ADDRESS

mem [CCSR_ADDR 0x814C] = 0x00000000

# DDR_TIMING_CFG_4

mem [CCSR_ADDR 0x8160] = 0x00000001

# DDR_TIMING_CFG_5

mem [CCSR_ADDR 0x8164] = 0x02401400

# DDR_ZQ_CNTL

mem [CCSR_ADDR 0x8170] = 0x89080600

# DDR_WRLVL_CNTL

mem [CCSR_ADDR 0x8174] = 0xc675f606

# DDR_SR_CNTR

mem [CCSR_ADDR 0x817c] = 0x00000000

# DDR_WRLVL_CNTL_2

mem [CCSR_ADDR 0x8190] = 0x06060607

# DDR_WRLVL_CNTL_3

mem [CCSR_ADDR 0x8194] = 0x08080807

# DDR_DDRCDR_1

mem [CCSR_ADDR 0x8b28] = 0x80040000

# DDR_DDRCDR_2

mem [CCSR_ADDR 0x8b2c] = 0x00000001

# DDR_ERR_DISABLE - DISABLE

mem [CCSR_ADDR 0x8e44] = 0x00000000

# DDR_ERR_SBE

mem [CCSR_ADDR 0x8e58] = 0x00000000

# delay before enable

wait 500

# DDR_SDRAM_CFG

mem [CCSR_ADDR 0x8110] = 0xc7040000

# wait for DRAM data initialization

wait 1500

##################################################################################

# eSPI Setup

# SPMODE

mem [CCSR_ADDR 0x110000] = 0x80000403

# SPIM - catch all events

mem [CCSR_ADDR 0x110008] = 0x00000000

# SPMODE0

mem [CCSR_ADDR 0x110020] = 0x2E170008

##################################################################################

# IFC Controller Setup

global ECC_EN

set ECC_ENC_EN 0x[format %x [expr $ECC_EN << 31]]

set ECC_DEC_EN 0x[format %x [expr $ECC_EN << 26]]

set NOR_CS 0

set NAND_CS 1

set CPLD_CS 2

# CPLD, addr 0xFFDF0000, 128K size, 8-bit, GPCM, Valid

# CSPR_EXT

mem [CCSR_ADDR [expr {0x12400C + $CPLD_CS * 0x0C}]] = 0x00000000

# CSPR

mem [CCSR_ADDR [expr {0x124010 + $CPLD_CS * 0x0C}]] = 0xFFDF0085

# AMASK

mem [CCSR_ADDR [expr {0x1240A0 + $CPLD_CS * 0x0C}]] = 0xFFFE0000

# CSOR

mem [CCSR_ADDR [expr {0x124130 + $CPLD_CS * 0x0C}]] = 0x00000000

# IFC_FTIM0

mem [CCSR_ADDR [expr {0x1241C0 + $CPLD_CS * 0x30}]] = 0xE00E000E

# IFC_FTIM1

mem [CCSR_ADDR [expr {0x1241C4 + $CPLD_CS * 0x30}]] = 0x0E001F00

# IFC_FTIM2

mem [CCSR_ADDR [expr {0x1241C8 + $CPLD_CS * 0x30}]] = 0x0E00001F

# IFC_FTIM3

mem [CCSR_ADDR [expr {0x1241CC + $CPLD_CS * 0x30}]] = 0x00000000

# NOR Flash, addr 0xE8000000, 128M size, 16-bit NOR

# CSPR_EXT

mem [CCSR_ADDR [expr {0x12400C + $NOR_CS * 0x0C}]] = 0x00000000

# CSPR

mem [CCSR_ADDR [expr {0x124010 + $NOR_CS * 0x0C}]] = 0xE8000101

# AMASK

mem [CCSR_ADDR [expr {0x1240A0 + $NOR_CS * 0x0C}]] = 0xF8000000

# CSOR

mem [CCSR_ADDR [expr {0x124130 + $NOR_CS * 0x0C}]] = 0x0000000C

# IFC_FTIM0

mem [CCSR_ADDR [expr {0x1241C0 + $NOR_CS * 0x30}]] = 0x40050005

# IFC_FTIM1

mem [CCSR_ADDR [expr {0x1241C4 + $NOR_CS * 0x30}]] = 0x35001A13

# IFC_FTIM2

mem [CCSR_ADDR [expr {0x1241C8 + $NOR_CS * 0x30}]] = 0x0410381C

# IFC_FTIM3

mem [CCSR_ADDR [expr {0x1241CC + $NOR_CS * 0x30}]] = 0x00000000

# NAND Flash, addr 0xFF800000, 64K size, 8-bit NAND

# CSPR_EXT

mem [CCSR_ADDR [expr {0x12400C + $NAND_CS * 0x0C}]] = 0x00000000

# CSPR

mem [CCSR_ADDR [expr {0x124010 + $NAND_CS * 0x0C}]] = 0xFF800083

# AMASK

mem [CCSR_ADDR [expr {0x1240A0 + $NAND_CS * 0x0C}]] = 0xFFFF0000

# CSOR

mem [CCSR_ADDR [expr {0x124130 + $NAND_CS * 0x0C}]] = 0x[format %x [expr 0x0110A100 | $ECC_ENC_EN | $ECC_DEC_EN]]

# IFC_FTIM0

mem [CCSR_ADDR [expr {0x1241C0 + $NAND_CS * 0x30}]] = 0x0E18070A

# IFC_FTIM1

mem [CCSR_ADDR [expr {0x1241C4 + $NAND_CS * 0x30}]] = 0x32390E18

# IFC_FTIM2

mem [CCSR_ADDR [expr {0x1241C8 + $NAND_CS * 0x30}]] = 0x01E0501E

# IFC_FTIM3

mem [CCSR_ADDR [expr {0x1241CC + $NAND_CS * 0x30}]] = 0x00000000

}

proc T1040RDB_init_core {} {

global master_core

variable CAM_GROUP "regPPCTLB1/"

variable SPR_GROUP "e5500 Special Purpose Registers/"

variable GPR_GROUP "General Purpose Registers/"

##################################################################################

#

# Memory Map

#

# 0x00000000 0x7FFFFFFF DDR 2G

# 0xE8000000 0xEFFFFFFF NOR 128M

# 0xF0000000 0xF03FFFFF DCSR 4M

# 0xFE000000 0xFEFFFFFF CCSR Space 16M

# 0xFF800000 0xFF80FFFF NAND 64K

# 0xFFDF0000 0xFFE0FFFF CPLD 128K

# 0xFFFFF000 0xFFFFFFFF Boot Page 4K

#

##################################################################################

# #################################################################################

# MMU initialization

# define 16M TLB entry 1 : 0xFE000000 - 0xFEFFFFFF for CCSR_ADDR cache inhibited, guarded

reg ${CAM_GROUP}L2MMU_CAM1 = 0x7000000A1C08000000000000FE00000000000000FE000001

# define 256M TLB entry 2 : 0xE8000000 - 0xEFFFFFFF for NOR cache inhibited, guarded

reg ${CAM_GROUP}L2MMU_CAM2 = 0x9000000A1C08000000000000E000000000000000E0000001

# define 1G TLB entry 3 : 0x00000000 - 0x3FFFFFFF for DDR cache inhibited

reg ${CAM_GROUP}L2MMU_CAM3 = 0xA00000081C08000000000000000000000000000000000001

# define 1G TLB entry 4 : 0x40000000 - 0x7FFFFFFF for DDR cache inhibited

reg ${CAM_GROUP}L2MMU_CAM4 = 0xA00000081C08000000000000400000000000000040000001

# define 4MB TLB entry 5 : 0xF0000000 - 0xF03FFFFF for DCSR cache inhibited, guarded

reg ${CAM_GROUP}L2MMU_CAM5 = 0x6000000A1C08000000000000F000000000000000F0000001

# define 256K TLB entry 6 : 0xFFDF0000 - 0xFFE0FFFF for CPLD cache inhibited, guarded

reg ${CAM_GROUP}L2MMU_CAM6 = 0x4000000A1C08000000000000FFDF000000000000FFDF0001

# define 64K TLB entry 7 : 0xFF800000 - 0xFF80FFFF for NAND cache inhibited, guarded

reg ${CAM_GROUP}L2MMU_CAM7 = 0x3000000A1C08000000000000FF80000000000000FF800001

# init board, only when the init is run for master core

variable proc_id [expr {[reg ${SPR_GROUP}PIR %d -np] >> 5 }]

if {$proc_id == $master_core} {

init_board

}

##################################################################################

# Interrupt vectors initialization

# interrupt vectors in RAM at 0x[expr {${proc_id} << 1}]0000000

# IVPR (default reset value)

reg ${SPR_GROUP}IVPR = 0x[expr {${proc_id} << 1}]0000000

# interrupt vector offset registers

# IVOR0 - critical input

reg ${SPR_GROUP}IVOR0 = 0x00000100

# IVOR1 - machine check

reg ${SPR_GROUP}IVOR1 = 0x00000200

# IVOR2 - data storage

reg ${SPR_GROUP}IVOR2 = 0x00000300

# IVOR3 - instruction storage

reg ${SPR_GROUP}IVOR3 = 0x00000400

# IVOR4 - external input

reg ${SPR_GROUP}IVOR4 = 0x00000500

# IVOR5 - alignment

reg ${SPR_GROUP}IVOR5 = 0x00000600

# IVOR6 - program

reg ${SPR_GROUP}IVOR6 = 0x00000700

# IVOR7 - floating point unavailable

reg ${SPR_GROUP}IVOR7 = 0x00000800

# IVOR8 - system call

reg ${SPR_GROUP}IVOR8 = 0x00000C00

# IVOR10 - decrementer

reg ${SPR_GROUP}IVOR10 = 0x00000900

# IVOR11 - fixed-interval timer interrupt

reg ${SPR_GROUP}IVOR11 = 0x00000F00

# IVOR12 - watchdog timer interrupt

reg ${SPR_GROUP}IVOR12 = 0x00000B00

# IVOR13 - data TLB errror

reg ${SPR_GROUP}IVOR13 = 0x00001100

# IVOR14 - instruction TLB error

reg ${SPR_GROUP}IVOR14 = 0x00001000

# IVOR15 - debug

reg ${SPR_GROUP}IVOR15 = 0x00001500

# IVOR35 - performance monitor

reg ${SPR_GROUP}IVOR35 = 0x00001900

##################################################################################

# Enable branch prediction

reg ${SPR_GROUP}BUCSR = 0x01400201

##################################################################################

# Debugger settings

# enable machine check

reg ${SPR_GROUP}HID0 = 0x80000000

# enable floating point

reg ${SPR_GROUP}MSR = 0x00002000

# infinite loop at program exception to prevent taking the exception again

mem v:0x[expr {${proc_id} << 1}]0000700 = 0x48000000

# prevent stack unwinding at entry_point/reset when stack pointer is not initialized

reg ${GPR_GROUP}SP = 0x0000000F

if {$proc_id == $master_core} {

# DCFG_BRR - enable all cores

mem [CCSR_ADDR 0xe00e4] = 0x0000000F

# RCPM_CTBENR - enable all cores' timebase

mem [CCSR_ADDR 0xe2084] = 0x0000000F

}

}

proc envsetup {} {

# Environment Setup

radix x

config hexprefix 0x

config MemIdentifier v

config MemWidth 32

config MemAccess 32

config MemSwap off

}

#-------------------------------------------------------------------------------

# Main

#-------------------------------------------------------------------------------

envsetup

T1040RDB_init_core

--

Gourav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Also, make sure you disable the controller first, then apply DDR configuration, then enable the controller. U mean to say DDR_DDR_SDRAM_CFG [MEM_EN]: 0 then set all DDR reg. and make it DDR_DDR_SDRAM_CFG [MEM_EN]: 1.

correct me if im wrong..

--

Gourav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are right.

Adrian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Adrian,

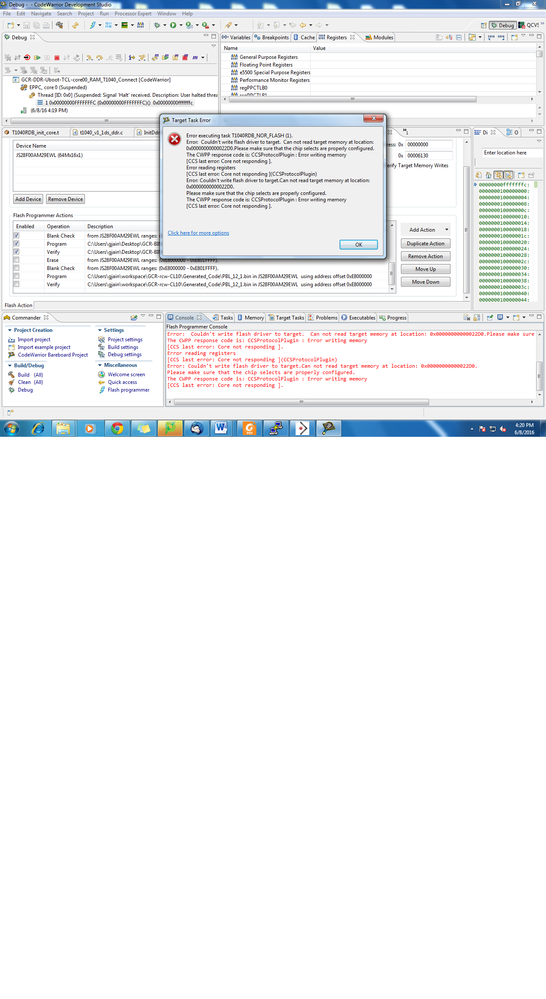

I have done changes as you suggested before. Copied ddr reg values in .tcl file and tried to fuse into NOR flash and got this error,

Here is my observation,

1) DDR reg values from SPD and from uboot both are not matching. why is it so?

=> md 0xfe008000

fe008000: 0000007f 00000000 00000000 00000000 ................

fe008010: 00000000 00000000 00000000 00000000 ................

fe008020: 00000000 00000000 00000000 00000000 ................

fe008030: 00000000 00000000 00000000 00000000 ................

fe008040: 00000000 00000000 00000000 00000000 ................

fe008050: 00000000 00000000 00000000 00000000 ................

fe008060: 00000000 00000000 00000000 00000000 ................

fe008070: 00000000 00000000 00000000 00000000 ................

fe008080: 80044302 00000000 00000000 00000000 ..C.............

fe008090: 00000000 00000000 00000000 00000000 ................

fe0080a0:00000000 00000000 00000000 00000000 ................

fe0080b0: 00000000 00000000 00000000 00000000 ................

fe0080c0: 00000000 00000000 00000000 00000000 ................

fe0080d0: 00000000 00000000 00000000 00000000 ................

fe0080e0: 00000000 00000000 00000000 00000000 ................

fe0080f0: 00000000 00000000 00000000 00000000 ................

=>

fe008100: 00060000 4011000c 6e6a0644 002880d0 ....@...nj.D.(..

fe008110: c7040000 00401900 00441420 00800000 .....@...D. ....

fe008120: 00000000 06180100 deadbeef 00000000 ................

fe008130: 02000000 00000000 00000000 00000000 ................

fe008140: 00000000 00000000 00000000 00000000 ................

fe008150: 00000000 00000000 00000000 00000000 ................

fe008160: 00000001 02401400 00000000 00000000 .....@..........

fe008170: 89080600 c675f606 00000000 00000000 .....u..........

fe008180: 00000000 00000000 00000000 00000000 ................

fe008190: 06060607 08080807 00000000 00000000 ................

fe0081a0: 00000000 00000000 00000000 00000000 ................

fe0081b0: 00000000 00000000 00000000 00000000 ................

fe0081c0: 00000000 00000000 00000000 00000000 ................

fe0081d0: 00000000 00000000 00000000 00000000 ................

fe0081e0: 00000000 00000000 00000000 00000000 ................

fe0081f0: 00000000 00000000 00000000 00000000 ................

=>

fe008200: 00001420 00800000 00000000 00000000 ... ............

fe008210: 00000000 00000000 00000000 00000000 ................

fe008220: 00000000 00000000 00000000 00000000 ................

fe008230: 00000000 00000000 00000000 00000000 ................

fe008240: 00000000 00000000 00000000 00000000 ................

fe008250: 00000000 00000000 00000000 00000000 ................

fe008260: 00000000 00000000 00000000 00000000 ................

fe008270: 00000000 00000000 00000000 00000000 ................

fe008280: 00000000 00000000 00000000 00000000 ................

fe008290: 00000000 00000000 00000000 00000000 ................

fe0082a0: 00000000 00000000 00000000 00000000 ................

fe0082b0: 00000000 00000000 00000000 00000000 ................

fe0082c0: 00000000 00000000 00000000 00000000 ................

fe0082d0: 00000000 00000000 00000000 00000000 ................

fe0082e0: 00000000 00000000 00000000 00000000 ................

fe008e70: 00000000 00000000 00000000 00000000 ................

fe008e80: 00000000 00000000 00000000 00000000 ................

fe008e90: 00000000 00000000 00000000 00000000 ................

fe008ea0: 00000000 00000000 00000000 00000000 ................

fe008eb0: 00000000 00000000 00000000 00000000 ................

fe008ec0: 00000000 00000000 00000000 00000000 ................

fe008ed0: 00000000 00000000 00000000 00000000 ................

fe008ee0: 00000000 00000000 00000000 00000000 ................

fe008ef0: 00000000 00000000 00000000 00000000 ................

DDR reg values from SPD :

# DDR Controller 1 Registers

# DDR_SDRAM_CFG

mem i:0xFE008110 = [value_of 0x47200008]

# CS0_BNDS

mem i:0xFE008000 = [value_of 0x7F]

# CS1_BNDS

mem i:0xFE008008 = [value_of 0x008000BF]

# CS2_BNDS

mem i:0xFE008010 = [value_of 0x0100013F]

# CS3_BNDS

mem i:0xFE008018 = [value_of 0x0140017F]

# CS0_CONFIG

mem i:0xFE008080 = [value_of 0x80014302]

# CS1_CONFIG

mem i:0xFE008084 = [value_of 0x00010202]

# CS2_CONFIG

mem i:0xFE008088 = [value_of 0x00010202]

# CS3_CONFIG

mem i:0xFE00808C = [value_of 0x00010202]

# CS0_CONFIG_2

mem i:0xFE0080C0 = [value_of 0x00]

# CS1_CONFIG_2

mem i:0xFE0080C4 = [value_of 0x00]

# CS2_CONFIG_2

mem i:0xFE0080C8 = [value_of 0x00]

# CS3_CONFIG_2

mem i:0xFE0080CC = [value_of 0x00]

# TIMING_CFG_3

mem i:0xFE008100 = [value_of 0x010C1000]

# TIMING_CFG_0

mem i:0xFE008104 = [value_of 0x8055000C]

# TIMING_CFG_1

mem i:0xFE008108 = [value_of 0xBCB48C67]

# TIMING_CFG_2

mem i:0xFE00810C = [value_of 0x00411120]

# DDR_SDRAM_CFG_2

mem i:0xFE008114 = [value_of 0x00401050]

# DDR_SDRAM_MODE

mem i:0xFE008118 = [value_of 0x00061A71]

# DDR_SDRAM_MODE_2

mem i:0xFE00811C = [value_of 0x00180000]

# DDR_SDRAM_MODE_2

mem i:0xFE00811C = [value_of 0x00180000]

# DDR_SDRAM_MODE_2

mem i:0xFE00811C = [value_of 0x00180000]

# DDR_SDRAM_MODE_3

mem i:0xFE008200 = [value_of 0x00]

# DDR_SDRAM_MODE_4

mem i:0xFE008204 = [value_of 0x00]

# DDR_SDRAM_MODE_5

mem i:0xFE008208 = [value_of 0x00]

# DDR_SDRAM_MODE_6

mem i:0xFE00820C = [value_of 0x00]

# DDR_SDRAM_MODE_7

mem i:0xFE008210 = [value_of 0x00]

# DDR_SDRAM_MODE_8

mem i:0xFE008214 = [value_of 0x00]

# DDR_SDRAM_MD_CNTL

mem i:0xFE008120 = [value_of 0x00000000]

# DDR_SDRAM_INTERVAL

mem i:0xFE008124 = [value_of 0x18600618]

# DDR_DATA_INIT

mem i:0xFE008128 = [value_of 0xDEADBEEF]

# DDR_SDRAM_CLK_CNTL

mem i:0xFE008130 = [value_of 0x02800000]

# DDR_INIT_ADDR

mem i:0xFE008148 = [value_of 0x00000000]

# DDR_INIT_EXT_ADDR

mem i:0xFE00814C = [value_of 0x00000000]

# TIMING_CFG_4

mem i:0xFE008160 = [value_of 0x00220001]

# TIMING_CFG_5

mem i:0xFE008164 = [value_of 0x04401400]

# DDR_ZQ_CNTL

mem i:0xFE008170 = [value_of 0x89080600]

# DDR_WRLVL_CNTL

mem i:0xFE008174 = [value_of 0x8655F609]

# DDR_SR_CNTR

mem i:0xFE00817C = [value_of 0x00000000]

# DDR_WRLVL_CNTL_2

mem i:0xFE008190 = [value_of 0x00]

# DDR_WRLVL_CNTL_3

mem i:0xFE008194 = [value_of 0x00]

# DDR_ERR_DISABLE

mem i:0xFE008E44 = [value_of 0x00]

# DDR_ERR_INT_EN

mem i:0xFE008E48 = [value_of 0x1D]

# DDR_ERR_SBE

mem i:0xFE008E58 = [value_of 0x00010000]

# DDRCDR_1

mem i:0xFE008B28 = [value_of 0x80000000]

# DDRCDR_2

mem i:0xFE008B2C = [value_of 0x00]

# DDR_SDRAM_CFG_3

mem i:0xFE008260 = [value_of 0x00]

# TIMING_CFG_6

mem i:0xFE008168 = [value_of 0x00]

# TIMING_CFG_7

mem i:0xFE00816C = [value_of 0x00]

# TIMING_CFG_8

mem i:0xFE008250 = [value_of 0x00]

# DESKEW_CNTL

mem i:0xFE0082A0 = [value_of 0x00]

# DQ_MAP0

mem i:DDRmc1_DQ_MAP0_ADDR = [value_of 0x00]

# DQ_MAP1

mem i:DDRmc1_DQ_MAP1_ADDR = [value_of 0x00]

# DQ_MAP2

mem i:DDRmc1_DQ_MAP2_ADDR= [value_of 0x00]

# DQ_MAP3

mem i:DDRmc1_DQ_MAP3_ADDR = [value_of 0x00]

# DDR_SDRAM_MODE_9

mem i:0xFE008220 = [value_of 0x00]

# DDR_SDRAM_MODE_10

mem i:0xFE008224 = [value_of 0x00]

# DDR_SDRAM_MODE_11

mem i:0xFE008228 = [value_of 0x00]

# DDR_SDRAM_MODE_12

mem i:0xFE00822C = [value_of 0x00]

# DDR_SDRAM_MODE_13

mem i:0xFE008230 = [value_of 0x00]

# DDR_SDRAM_MODE_14

mem i:0xFE008234 = [value_of 0x00]

# DDR_SDRAM_MODE_15

mem i:0xFE008238 = [value_of 0x00]

# DDR_SDRAM_MODE_16

mem i:0xFE00823C = [value_of 0x00]

# DDR_SDRAM_RCW_3

mem i:0xFE0081A0 = [value_of 0x00]

# DDR_SDRAM_RCW_4

mem i:0xFE0081A4 = [value_of 0x00]

# DDR_SDRAM_RCW_5

mem i:0xFE0081A8 = [value_of 0x00]

# DDR_SDRAM_RCW_6

mem i:0xFE0081AC = [value_of 0x00]

pls look into this file and let me know where i need to make changes..

--

Gourav

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The differences between T1040RDB_init_core.tcl and T1040RDB_init_sram.tcl, is that the first one do the initialization for DDR, SRAM, NOR but the second one will except DDR.

To have T1040RDB_init_core.tcl work properly, you have to initialize correct the DDR controller. You can take the values for ddr registers from uboot, if uboot works fine on your board. You can to that by attaching to the uboot from CW and get the DDR values or dump the regs values from uboot. Also, make sure you disable the controller first, then apply DDR configuration, then enable the controller.

Adrian