- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for QorIQ

- :

- Need urgent help - P1013 JTAG and Bank 0 access not working

Need urgent help - P1013 JTAG and Bank 0 access not working

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Need urgent help - P1013 JTAG and Bank 0 access not working

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a board with P1013 processor and need urgent help resolving issue below.

I have setup the BOOT option for LB FCM 8-bit NAND Flash Small page.

CKSTP_OUT0_N = '1' (4.7K pull-up boot strap)

CKSTP_OUT1_N = '0' (4.7K pull-down boot strap)

ETH_PHY_TXD1 = '0' (4.7K pull-down boot strap)

GPP_READY_P0 = '0' (4.7K pull-down boot strap)

When accessing the device via JTAG, I get an error. See attachment. Please help me understand why required boot strapping pull-down on CKSTP_OUT1_N is causing error on JTAG.

If I remove the pull-down on CKSTP_OUT1_N, I am able to access the device via JTAG.

After accessing the JTAG any, we tried to access Bank 0 as we have NAND flash connected to Bank 0. However, it fails. That is, I don't see any activity on Chip Select 0, Write enable, output enable on FCM interface. However, when I access Bank 1, i see activity on all the signals. Please help me understand what setting am I missing to Bank 0 access.

Following is how we are configured the registers in regards to FCM/NAND Flash

#define CONFIG_NAND_ADDR_BOOT 0xEFF00000

// LAWBAR6 - Local Bus NAND (boot)

// bit 8 - 31 = 0xEFF00000 - base addr

MM_LAWBAR6 = CONFIG_NAND_ADDR_BOOT >> 12;

// LAWAR6

// bit 0 = 1 - enable window

// bit 7-11 = 00100 - Local Bus

// bit 26-31 = 001111 64k - size

MM_LAWAR6 = 0x8040000f;

// CS0 - NAND Flash (boot)

// BR0 base address at 0xEFF00000, port size 8 bit, FCM

eLBC_BR0 = 0xf8001001;// OR0 64KB flash size, FCM (large page NAND Flash)

eLBC_ORf0 = 0xf8000ff7;

Regards,

Amit

Original Attachment has been moved to: target-init-fail.txt.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Amit,

The CKSTP_OUT pin is an output that tell external hardware that the processor is in a checkstop state, it is not used by the debugger, it is recommended with 10K pull up. The pin itself does not cause the reset, a reset will put CKSTP_OUT in high-Z and the recommended pull-up will ensure the signal is negated after the reset sequence is complete.

For bank0 NAND Flash accessing problem, there is problem with BR0 and OR0 registers configuration in your description.

Please refer to the following configuration from CodeWarrior initialization file.

# BR0 base address at 0xEFF00000, port size 8 bit, FCM, ECC checking and generation are disabled

mem [CCSR 0x5000] = 0x[format %x [expr 0xEFF00821 | $ECC_EN]]

if {$ROM_LOC == $FCM_SMALL_PAGE_BOOT_LOC} {

# boot from fcm small page boot location

# OR0 64KB flash size, FCM (small page NAND Flash)

mem [CCSR 0x5004] = 0xFFFF0796

} else {

# boot from fcm large page boot location

# OR0 64KB flash size, FCM (large page NAND Flash)

mem [CCSR 0x5004] = 0xFFFF07AE

}

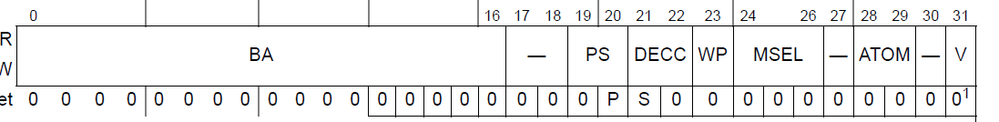

Please refer to the following BR and OR registers definition, for details please refer to the processor reference user manual.

Base Registers definition is similar as the above

BA: Base address.

PS:Port Size

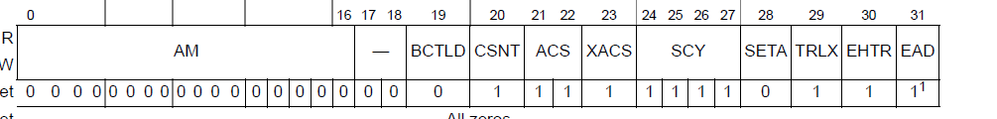

Option Register definition is as the following.

AM: GPCM address mask.

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------