- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- What should the DEVICE_TYPE mode setting be for PCIe root complex?

What should the DEVICE_TYPE mode setting be for PCIe root complex?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

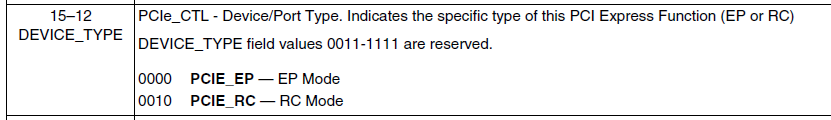

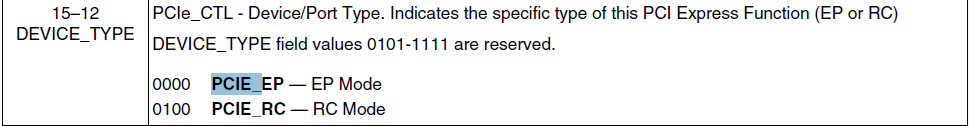

For the iMX6SDL, the Linux PCIe driver sets the DEVICE_TYPE in GPR12 to 0x4 for RC mode: // set device type to RC (PCI_EXP_TYPE_ROOT_PORT=4 is from pcie_regs.h)

imx_pcie_clrset(iomuxc_gpr12_device_type, PCI_EXP_TYPE_ROOT_PORT << 12, IOMUXC_GPR12

);

This seems odd since the ref manual says that 0x2 is the proper value for RC mode:

0000 PCIE_EP — EP Mode

0010 PCIE_RC — RC Mode

Can anyone explain why that it is? And how it is that it works that way? Wondering what setting I should use for an RTOS version of the driver I'm creating.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Tyler,

It is a typo mistake in RM doc, would be fixed in later version. The BSP code is right.

i.MX 6Dual/6Quad Applications Processor Reference Manual

Document Number: IMX6DQRM - Rev. 3, 07/2015

It has being corrected on some of our newer devices, documentation… This has being corrected on our imx6slx documentation as you can see below..

i.MX 6SoloX Applications Processor Reference Manual

Document Number: IMX6SXRM, Rev 0, 2/2015

Best Regards,

Norbel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

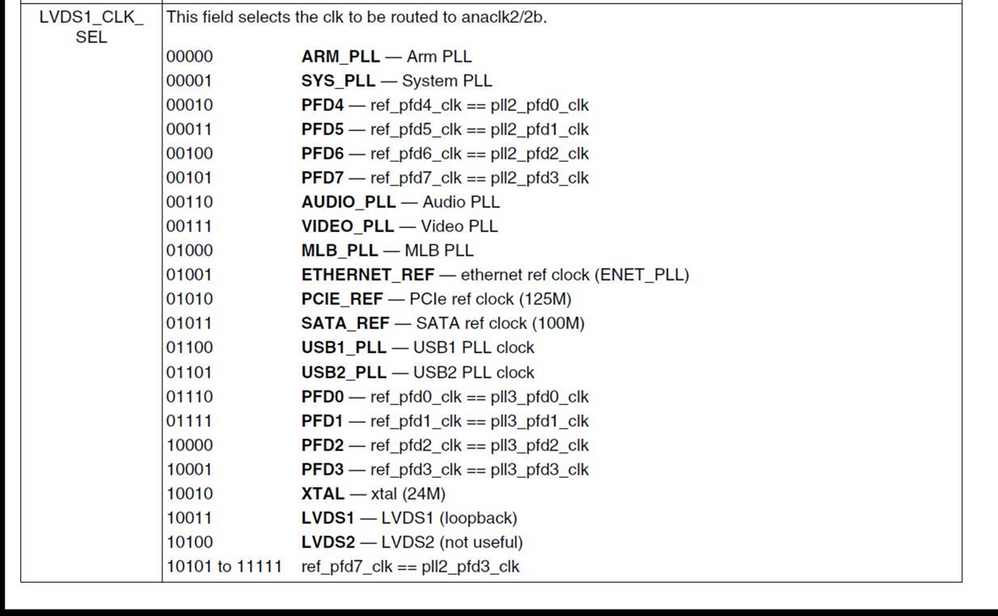

Follow up question on a similar issue - the LVDS1_CLK_SEL field in the CCM_ANALOG_MISC1 register...

Linux sets this to be 0x8000040B ( so 0b01011 for that field) which is not present in the list:

00000 ARM_PLL — Arm PLL

00001 SYS_PLL — System PLL

00010 PFD4 — ref_pfd4_clk == pll2_pfd0_clk

00011 PFD5 — ref_pfd5_clk == pll2_pfd1_clk

00100 PFD6 — ref_pfd6_clk == pll2_pfd2_clk

00101 PFD7 — ref_pfd7_clk == pll2_pfd3_clk

00110 AUDIO_PLL — Audio PLL

00111 VIDEO_PLL — Video PLL

01000 MLB_PLL — MLB PLL

01001 ETHERNET_REF — ethernet ref clock (ENET_PLL)

01010 PCIE_REF — PCIe ref clock (125M)

01100 USB1_PLL — USB1 PLL clock

01101 USB2_PLL — USB2 PLL clock

01110 PFD0 — ref_pfd0_clk == pll3_pfd0_clk

01111 PFD1 — ref_pfd1_clk == pll3_pfd1_clk

10000 PFD2 — ref_pfd2_clk == pll3_pfd2_clk

10001 PFD3 — ref_pfd3_clk == pll3_pfd3_clk

10010 XTAL — xtal (24M)

10011 LVDS1 — LVDS1 (loopback)

10100 LVDS2 — LVDS2 (not useful)

10101 to 11111 ref_pfd7_clk == pll2_pfd3_clk

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Tyler,

Please take a look at latest RM, it shows 01011 as “SATA_REF – SATA ref clock(100M)”

Selection 01011 is associated with SATA on the 6DQ. But SATA doesn't exist on either the 6SDL or the 6SL.

As I understand it if you set the value 01011 it enables the 100Mhz differential clock, even if SATA module is not on device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Tyler,

It is a typo mistake in RM doc, would be fixed in later version. The BSP code is right.

i.MX 6Dual/6Quad Applications Processor Reference Manual

Document Number: IMX6DQRM - Rev. 3, 07/2015

It has being corrected on some of our newer devices, documentation… This has being corrected on our imx6slx documentation as you can see below..

i.MX 6SoloX Applications Processor Reference Manual

Document Number: IMX6SXRM, Rev 0, 2/2015

Best Regards,

Norbel