- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- imx6q Jtag init ram failed

imx6q Jtag init ram failed

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

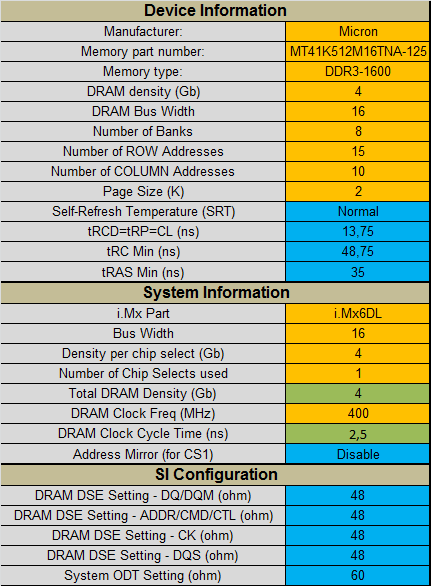

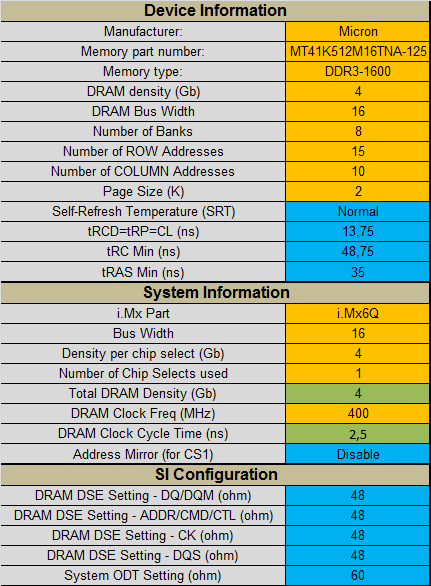

i'm trying to initialize my DDR3L using the values generated by DDR3 script aid v0.10, but i'm not able to read any registers by jtag.

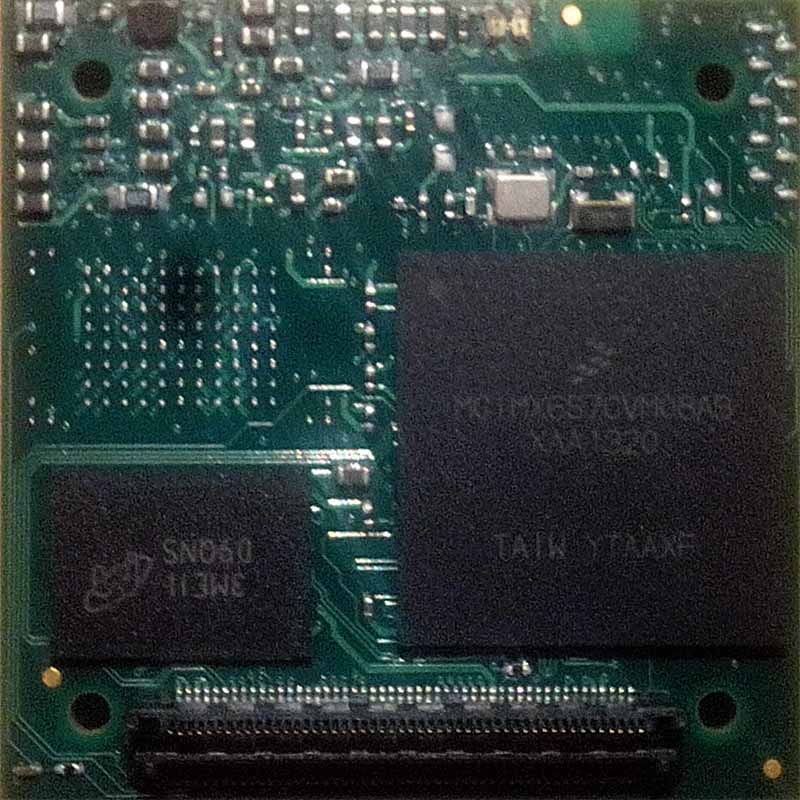

The SDRAM model is MT41K512M16_DDR3L_8Gb_x16_2CS_TwinDie_V80A

I configured the script as:

Is it correct? I have the dought about the chip select.

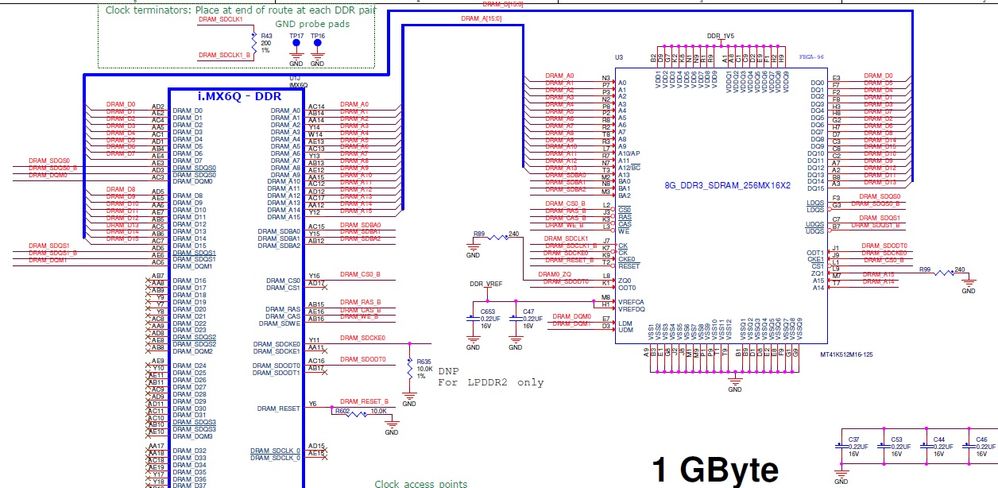

In the schematic i see the i.MX6Q - DDR module has only DRAM_CS0 connected to CS0 and CS1 MT41K512M16 module.

I see if i use the configuration of Nitrogen6x board, i'm able to read and write the registers.

Thanks

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fausto

script usage is described in presentation DRAM Controller Optimization

for i.MX Application Processors :

https://community.freescale.com/docs/DOC-104363

also : what reference design is based your board. Do you mean that

you are using DDR memory 16bit width with i.MX6Q, what is the reason ?

Attached is 16 bit example, one can look at other Sabre SD DDR init scripts on

https://community.freescale.com/docs/DOC-105652

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fausto

script usage is described in presentation DRAM Controller Optimization

for i.MX Application Processors :

https://community.freescale.com/docs/DOC-104363

also : what reference design is based your board. Do you mean that

you are using DDR memory 16bit width with i.MX6Q, what is the reason ?

Attached is 16 bit example, one can look at other Sabre SD DDR init scripts on

https://community.freescale.com/docs/DOC-105652

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Yes i use Imx6q and 16bit because my board is very small (44cm x 44cm)

The schematic is:

I found a HW problem ( i missed to connect the ODT[1:0],Chip Select and CKE1 for TwinDie memory).

My questions are:

1)Can i use only the half memory (512KB) before patching the board?

2)which is the right configuration of DDR3 script aid v0.10? I'm trying multiple choises but the board doesn't work. The attached 16 bit example works but why? You give me a generic configuration where the micro was imx6DL and not imx6q, and the DDR3 are different. I'm confused.

thanks a lot

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fausto

1. yes

2. i.MX6DL and i.MX6Q have similar MMDC modules. For configuration of

DDR3 script aid v0.10 one can look at presentation DRAM Controller Optimizationfor

i.MX Application Processors, it gives example for SDB board. Then change settings

for custom board.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

now i'm able to init the ram using the configuration generated by DDR3 script aid v0.10.

I used the configuration of MT41K256M16 / 4Gb ( MT41K512M16 / 8Gb) to int half memory (as you suggested me)

If i try to write and read the PC register i have 2 different behaviours:

i.Mx6DL

(gdb) mon imx6.cpu.0 mdw 0x17800000 0x04

0x17800000 d2192a00 82100655 84028205 4210de02 .*..U..........B

(gdb) mon imx6.cpu.0 mww 0x17800000 0x123456ab 0x04

(gdb) mon imx6.cpu.0 mdw 0x17800000 0x10

0x17800000 123456ab 123456ab 123456ab 123456ab .V4..V4..V4..V4.

i.Mx6Q

(gdb) mon imx6.cpu.0 mdw 0x17800000 0x04

0x17800000 ff7dff9e 9c1c1b37 dbb8cf65 2bdf8f0d ..}.7...e......+

(gdb) mon imx6.cpu.0 mww 0x17800000 0x123456ab 0x04

(gdb) mon imx6.cpu.0 mdw 0x17800000 0x10

0x17800000 ff34ffab 123456ab 123456ab 123456ab ..4..V4..V4..V4.

if you take a look the reading, you can see hte first 64bits ( ff34ffab instead of 123456ab ) are wrong when i set i.Mx6Q.

My question is:

Why the configuration works fine if i set Mx6DL instead of Mx6Q? My Micro is Mx6Q and not Mx6DL.

Thank you

Fausto

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Now the i.Mx6Q works fine if i change the following registers from 0 value to:

//For target board, may need to run write leveling calibration to fine tune these settings

| mww phys | 0x021b080c | 0x0040003C |

//Read DQS Gating calibration

| mww phys | 0x021b083c | 0x42350231 |

I get those values from another configuration file found in internet.

Why doesn't the debugger work fine if those 2 registers are set to 0?

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

please check AN4467 i.MX 6 Series DDR Calibration

http://www.nxp.com/files/32bit/doc/app_note/AN4467.pdf

~igor