- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MQX Software Solutions

- :

- MQX Software Solutions

- :

- MQX_UNHANDLED_INTERRUPT(0x0041) after setting a GPIO pin

MQX_UNHANDLED_INTERRUPT(0x0041) after setting a GPIO pin

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone.

I am getting this problem when I set an output pin on a K20 using

GPIO_DRV_SetPinOutput() function.

This pin enables the power for a section on my board, so I checked if voltage dips are happening on the rail powering the K20 when switching. A 2 mV dip is appearing so I think the problem is not because a power fluctuation.

I am using MQX 4.2.

Any way to know what is going on?

Thanks,

Jose

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

Thanks for your time David. I am using K20DN512VLL10.

The problem was NMI input. It was being set by the modem and NMI interrupt was happening.

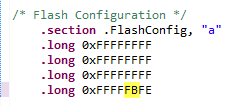

I disabled NMI interrupt modifying flash configuration word in startup_MK20D10.s and now everything is ok.

Thanks !!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi.

Thanks for your time David. I am using K20DN512VLL10.

The problem was NMI input. It was being set by the modem and NMI interrupt was happening.

I disabled NMI interrupt modifying flash configuration word in startup_MK20D10.s and now everything is ok.

Thanks !!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Glad you found the issue and shared it with us.

Regards,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jose,

Please check that you have enable the clock to the desired GPIO module in the SIM module SCGC5 register before trying to access any GPIO registers. If clock to module is not enabled, when you access a module register you get exception to occur.

Regards,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David.

The ports are properly clocked.

When this pin is set, an onboard GSM modem is powered and a 2 amps spike is drawn by the modem.

This power spike might be causing the exception.

How can I do to find out the source of the exception and being able to handle it?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jose,

Glad GPIO clocks enabled OK.

Yes a large current draw could cause the K20 (which K20 device are you using?) to reset.

The Kinetis devices have a low-voltage detect (LVD) capability. When voltage gets below specific value, the device will reset.

In the reference manual there is a Reset and Boot chapter. It details what registers to look at.

6.2.2.2 Low-voltage detect (LVD)

The chip includes a system for managing low voltage conditions to protect memory

contents and control MCU system states during supply voltage variations. The system

consists of a power-on reset (POR) circuit and an LVD circuit with a user-selectable trip

voltage. The LVD system is always enabled in normal run, wait, or stop mode. The LVD

system is disabled when entering VLPx, LLS, or VLLSx modes.

The LVD can be configured to generate a reset upon detection of a low voltage condition

by setting the PMC's LVDSC1[LVDRE] bit to 1. The low voltage detection threshold is

determined by the PMC's LVDSC1[LVDV] field. After an LVD reset has occurred, the

LVD system holds the MCU in reset until the supply voltage has risen above the low

voltage detection threshold. The RCM's SRS0[LVD] bit is set following either an LVD

reset or POR.

Also chapter on Power Management Controller:

15.3 Low-voltage detect (LVD) system

This device includes a system to guard against low-voltage conditions. This protects

memory contents and controls MCU system states during supply voltage variations.

....

Regards,

David