- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Setting incoming interrupt from micrel ksz9021rn to GPIO

Setting incoming interrupt from micrel ksz9021rn to GPIO

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Setting incoming interrupt from micrel ksz9021rn to GPIO

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

I've an iMX6Q custom board using a micrel ksz9021rn gigabit ethernet, mostly working ok. However I'm now looking how to feed the INT_N interrupt output pin to the SoC ENET_RXD1 pin in order to set correctly the GPIO01_IO26 as input interrupt to the PHY. I know that my DTS has to be set as:

&fec {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet>;

phy-mode = "rgmii";

phy-reset-gpios = <&gpio1 25 0>;

txen-skew-ps = <0>;

txc-skew-ps = <3000>;

rxdv-skew-ps = <0>;

rxc-skew-ps = <3000>;

rxd0-skew-ps = <0>;

rxd1-skew-ps = <0>;

rxd2-skew-ps = <0>;

rxd3-skew-ps = <0>;

txd0-skew-ps = <0>;

txd1-skew-ps = <0>;

txd2-skew-ps = <0>;

txd3-skew-ps = <0>;

interrupts-extended = <&gpio1 26 IRQ_TYPE_LEVEL_HIGH>,

<&intc 0 119 IRQ_TYPE_LEVEL_HIGH>;

status = "okay";

};

interrupt-extended is actually commented out because doesn't work and end up in a kernel crash. My current iomuxc is set has below

janas-imx6q {

pinctrl_enet: enetgrp {

fsl,pins = <

MX6QDL_PAD_ENET_MDIO__ENET_MDIO 0x100b0

MX6QDL_PAD_ENET_MDC__ENET_MDC 0x100b0

MX6QDL_PAD_RGMII_TXC__RGMII_TXC 0x100b0

MX6QDL_PAD_RGMII_TD0__RGMII_TD0 0x100b0

MX6QDL_PAD_RGMII_TD1__RGMII_TD1 0x100b0

MX6QDL_PAD_RGMII_TD2__RGMII_TD2 0x100b0

MX6QDL_PAD_RGMII_TD3__RGMII_TD3 0x100b0

MX6QDL_PAD_RGMII_TX_CTL__RGMII_TX_CTL 0x100b0

MX6QDL_PAD_ENET_REF_CLK__ENET_TX_CLK 0x100b0

MX6QDL_PAD_RGMII_RXC__RGMII_RXC 0x1b0b0

MX6QDL_PAD_RGMII_RD0__RGMII_RD0 0x1b0b0

MX6QDL_PAD_RGMII_RD1__RGMII_RD1 0x1b0b0

MX6QDL_PAD_RGMII_RD2__RGMII_RD2 0x1b0b0

MX6QDL_PAD_RGMII_RD3__RGMII_RD3 0x1b0b0

MX6QDL_PAD_RGMII_RX_CTL__RGMII_RX_CTL 0x1b0b0

/* Phy reset */

MX6QDL_PAD_ENET_CRS_DV__GPIO1_IO25 0x000b0

/* Interrupt */

MX6QDL_PAD_ENET_RXD1__GPIO1_IO26 0x000b1

>;

};

I know the setup of RXD1__GPIO1_IO26 is wrong because I'll have to force SION bit for it. Then I looked at imx6q sabrelite implementation that uses this #define below to specify the iomuxc for the same purpose.

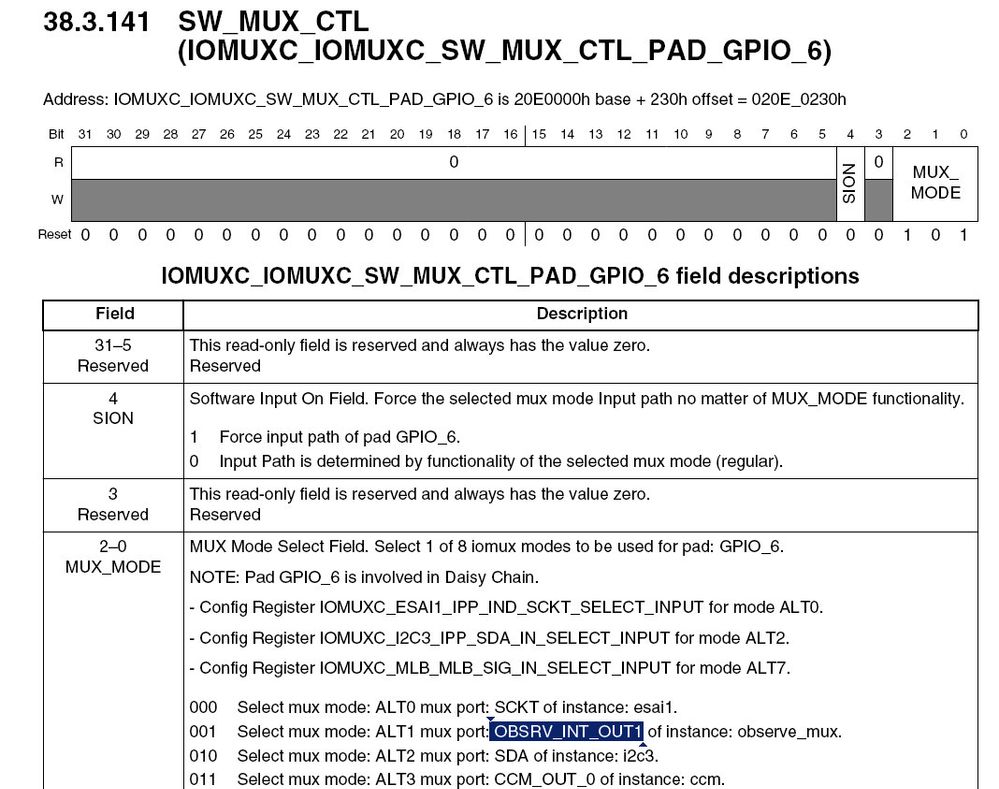

#define MX6QDL_PAD_GPIO_6__ENET_IRQ 0x230 0x600 0x03c 0x11 0xff000609

So my question is what is the 0x03c SELECT_INPUT register since I don't find it in the reference manual?

In my case likely I'll have to setup my GPIO1_IO26 as below and replace MX6QDL_PAD_ENET_RXD1__GPIO1_IO26 with the new MX6QDL_PAD_ENET_RXD1__ENET_IRQ:

#define MX6QDL_PAD_ENET_RXD1__ENET_IRQ 0x1e0 0x4f4 ???? 0x11 0xff000609 (???)

But I'm not sure about the 3rd param and if the 5th looks correct or not.

Any one can help?

Thanks in advance,

Roberto Fichera.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Roberto

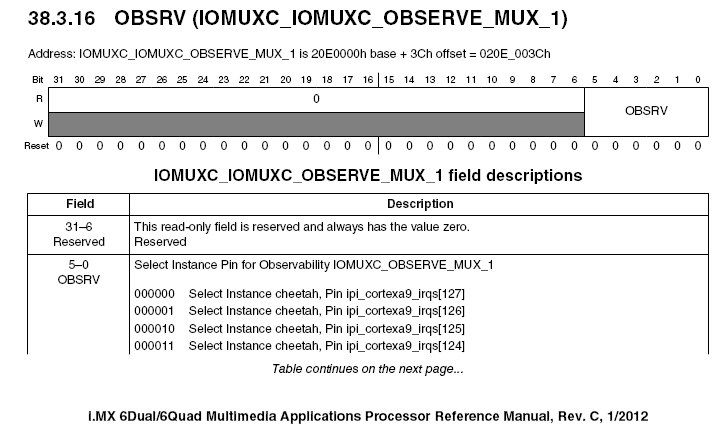

according to ERR006687 erratum interrupts can be selected by MUX and outputted

to pad GPIO6 using special IOMUXC_OBSERVE_MUX_1 register (used for

debugging purposes), its address offset is 3Ch. Unfortunately output of this

register can be muxed only on GPIO_6 pad.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

The errata ERR006687 you posted is referencing to workaround when the system enter in Wait mode hence will not get wakeup in case of ENET RX/TX traffic because the GPC doesn't see the interrupt.

If I set SION bit to GPIO1_26 wired to ksz9021 INT_N pin, I'm getting this kernel backtrace, should I set manually the direction of the GPIO instead to use SION bit then?

[ 2.311321] irq 54: nobody cared (try booting with the "irqpoll" option)

[ 2.318042] CPU: 0 PID: 0 Comm: swapper/0 Not tainted 4.4.0-fslc+ge79731d #1

[ 2.325099] Hardware name: Freescale i.MX6 Quad/DualLite (Device Tree)

[ 2.331634] Backtrace:

[ 2.334125] [<80014320>] (dump_backtrace) from [<80014514>] (show_stack+0x18/0x1c)

[ 2.341702] r7:00000036 r6:00000000 r5:80706208 r4:00000000

[ 2.347447] [<800144fc>] (show_stack) from [<8025b450>] (dump_stack+0x8c/0xa4)

[ 2.354685] [<8025b3c4>] (dump_stack) from [<8007e7e0>] (__report_bad_irq+0x2c/0xc8)

[ 2.362432] r7:00000036 r6:00000000 r5:00000000 r4:ee95f100

[ 2.368170] [<8007e7b4>] (__report_bad_irq) from [<8007ebec>] (note_interrupt+0x284/0x2e4)

[ 2.376438] r7:00000036 r6:00000000 r5:00000000 r4:ee95f100

[ 2.382177] [<8007e968>] (note_interrupt) from [<8007bfb8>] (handle_irq_event_percpu+0xcc/0x13c)

[ 2.390966] r10:80735c00 r9:ee95f100 r8:00000036 r7:00000000 r6:00000000 r5:00000000

[ 2.398886] r4:00000000 r3:00000000

[ 2.402504] [<8007beec>] (handle_irq_event_percpu) from [<8007c068>] (handle_irq_event+0x40/0x64)

[ 2.411380] r10:80f362b0 r9:ee95b610 r8:00000001 r7:806f1f00 r6:ee95f110 r5:ee95f160

[ 2.419299] r4:ee95f100

[ 2.421862] [<8007c028>] (handle_irq_event) from [<8007f328>] (handle_level_irq+0xc8/0x158)

[ 2.430218] r7:806f1f00 r6:ee95f110 r5:ee95f160 r4:ee95f100

[ 2.435955] [<8007f260>] (handle_level_irq) from [<8007b548>] (generic_handle_irq+0x28/0x3c)

[ 2.444396] r7:806f1f00 r6:04000000 r5:04000000 r4:0000001a

[ 2.450139] [<8007b520>] (generic_handle_irq) from [<80291a1c>] (mxc_gpio_irq_handler+0x38/0x104)

[ 2.459023] [<802919e4>] (mxc_gpio_irq_handler) from [<80291b54>] (mx3_gpio_irq_handler+0x6c/0xc0)

[ 2.467986] r10:804f4fc0 r9:ee808000 r8:00000001 r7:806f1f00 r6:806f7850 r5:ee95b510

[ 2.475905] r4:ee95b610

[ 2.478465] [<80291ae8>] (mx3_gpio_irq_handler) from [<8007b548>] (generic_handle_irq+0x28/0x3c)

[ 2.487253] r7:806f1f00 r6:806f2a34 r5:0000001b r4:806eb5fc

[ 2.492991] [<8007b520>] (generic_handle_irq) from [<8007b864>] (__handle_domain_irq+0x6c/0xe8)

[ 2.501702] [<8007b7f8>] (__handle_domain_irq) from [<800095d8>] (gic_handle_irq+0x48/0x94)

[ 2.510057] r9:f4001100 r8:806f2ba4 r7:f4000100 r6:80706480 r5:806f1e00 r4:f400010c

[ 2.517899] [<80009590>] (gic_handle_irq) from [<800150b8>] (__irq_svc+0x58/0x78)

[ 2.525389] Exception stack(0x806f1e00 to 0x806f1e48)

[ 2.530454] 1e00: 00000001 00000000 00000000 806f5278 00000082 00000000 806f0000 00000000

[ 2.538642] 1e20: 00000001 ee808000 804f4fc0 806f1e94 806f1e20 806f1e50 8006ec8c 8002d7f0

[ 2.546824] 1e40: 60000113 ffffffff

[ 2.550317] r9:ee808000 r8:00000001 r7:806f1e34 r6:ffffffff r5:60000113 r4:8002d7f0

[ 2.558162] [<8002d730>] (__do_softirq) from [<8002dd20>] (irq_exit+0xc4/0x138)

[ 2.565475] r10:804f4fc0 r9:ee808000 r8:00000001 r7:00000000 r6:806f2a34 r5:00000000

[ 2.573393] r4:806eb5fc

[ 2.575953] [<8002dc5c>] (irq_exit) from [<8007b86c>] (__handle_domain_irq+0x74/0xe8)

[ 2.583788] r5:00000000 r4:806eb5fc

[ 2.587406] [<8007b7f8>] (__handle_domain_irq) from [<800095d8>] (gic_handle_irq+0x48/0x94)

[ 2.595761] r9:f4001100 r8:806f2ba4 r7:f4000100 r6:80706480 r5:806f1f00 r4:f400010c

[ 2.603599] [<80009590>] (gic_handle_irq) from [<800150b8>] (__irq_svc+0x58/0x78)

[ 2.611088] Exception stack(0x806f1f00 to 0x806f1f48)

[ 2.616149] 1f00: 00000001 00000001 00000000 806f5278 806f0000 806f2908 00000000 806f28bc

[ 2.624336] 1f20: 806ea3e4 00000001 804f4fc0 806f1f5c 806f1f20 806f1f50 8006ed10 80010820

[ 2.632518] 1f40: 20000013 ffffffff

[ 2.636012] r9:00000001 r8:806ea3e4 r7:806f1f34 r6:ffffffff r5:20000013 r4:80010820

[ 2.643855] [<800107f8>] (arch_cpu_idle) from [<800696b8>] (default_idle_call+0x28/0x38)

[ 2.651956] [<80069690>] (default_idle_call) from [<800697d8>] (cpu_startup_entry+0x110/0x1b0)

[ 2.660585] [<800696c8>] (cpu_startup_entry) from [<804eb3b0>] (rest_init+0x12c/0x16c)

[ 2.668506] r7:806f2800 r4:80735b4c

[ 2.672134] [<804eb284>] (rest_init) from [<806a0cc8>] (start_kernel+0x360/0x3d4)

[ 2.679620] r5:ffffffff r4:8073614c

[ 2.683243] [<806a0968>] (start_kernel) from [<1000807c>] (0x1000807c)

[ 2.689776] r10:00000000 r9:412fc09a r8:1000406a r7:806f6b4c r6:806dea44 r5:806f28ac

[ 2.697695] r4:80736394

[ 2.700249] handlers:

[ 2.702535] [<80376fc4>] fec_enet_interrupt

[ 2.706744] Disabling IRQ #54

[ 2.739211] fec 2188000.ethernet (unnamed net_device) (uninitialized): MDIO write timeout

[ 2.769203] fec 2188000.ethernet (unnamed net_device) (uninitialized): MDIO write timeout

[ 2.799201] fec 2188000.ethernet (unnamed net_device) (uninitialized): MDIO write timeout

[ 2.829199] fec 2188000.ethernet (unnamed net_device) (uninitialized): MDIO write timeout

[ 2.859196] fec 2188000.ethernet (unnamed net_device) (uninitialized): MDIO write timeout

[ 2.889211] fec 2188000.ethernet (unnamed net_device) (uninitialized): MDIO read timeout

[ 2.900456] fec: probe of 2188000.ethernet failed with error -5

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Roberto

please create service request for obtaining document.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

thanks for pointing me this out. Can you please post the link where I can download the iMX6QDL Multimedia Application Processor Reference Manual because this is not documented at all in my Application Processor Reference Manual?

Thanks in advance,

Roberto Fichera.