- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- Timer

Timer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Timer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have one clarification on Timer usage. Currently, I am using "S912XEG128W1MAA".

For OS system timer, I have configured related registers as follows.

In Datasheet, fomular for the time-out period = (PITMTLD + 1) * (PITLD + 1) / fBUS

In Implementation,

.- PITMTLD(clock divider) : 47

.- PITLD(timeout counter) : 1000

.- fBUS : 48 MHz

With this configuration, I assumed 1000us timer to call a routine every 1000us.

Herewith, one confusion with the fomular from my side is..

Do I need to configure PITLD as 999 not 1000 to have 1000us cycle time?

Thanks and best regards,

Wongeun Chang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Wongeun Chang,

Yes, configure PITLD as 999 .

48*1000/48MHZ = 1000us

Hope it helps

Have a great day,

Alice Yang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice,

Thank you for your reply very much.

from my point of view, PITLD needs to be designed to be used as it is.

for example, if I configure to 1000, then it needs to be managed as 1000 us. Which means the use does not need to consider ‘-1’.

What do you think about it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry i don't know what's your meaning .

If you configure PITLD as 1000, then after 1000us , it will generate interrupt.

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Okay. Let me explain it in this way then,

Earlier, I asked following question regarding ‘Timer’.

1. The formula for the time-out period = (PITMTLD + 1) * (PITLD + 1) / fBUS

2. If PITMTLD = 47, fBUS = 48MHz, PITLD = 999

Timeout = (471)*(9991)/(48*10^6) = 1000us

3. Timeout flag seems to be set after 1000us.

4. In conclusion, setting PITLD to 999 means that timeout flag will be set every 1000us.

Q. When PITTf.p0 will be set to 1?

Case1. PITLD0 = 1000 -> 1000us or 1001us

Case2. PTILD0 = 999 -> 999 us or 1000us

BR Wongeun

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wongeun,

According to RM (chapter 17.4.1 Timer):

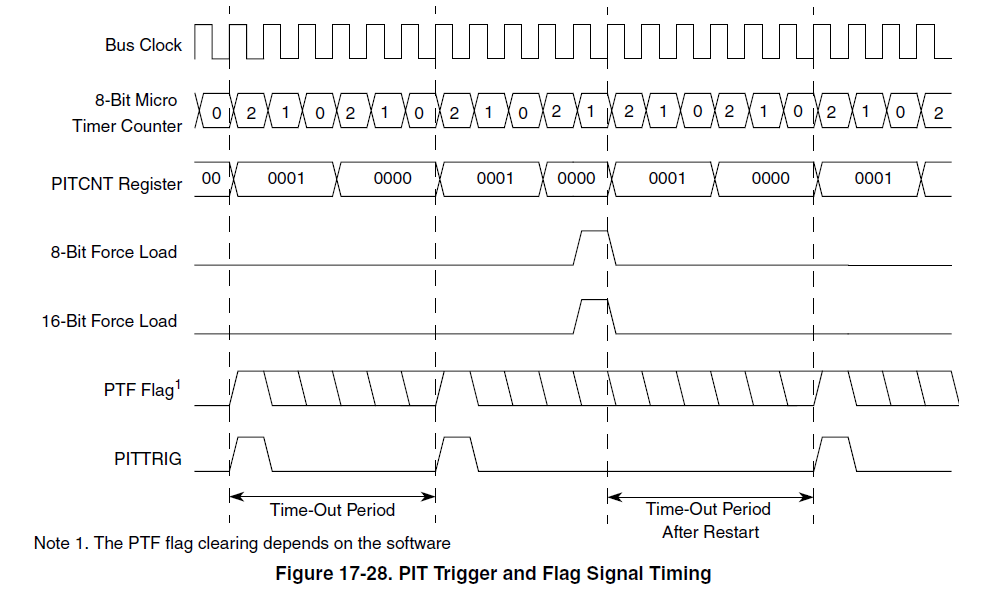

“Whenever a 16-bit timer counter and the connected 8-bit micro timer counter have counted to zero, the PITLD register is reloaded and the corresponding time-out flag PTF in the PIT time-out flag (PITTF) register is set, as shown in Figure 17-28.”

Therefore, PTFx flag is set when modulus down counter is reloaded from 0x0000 to PITLDx value.

Since value 0x0000 is also the valid value for modulus down counter, we have to set (time interval in us-1) as PITLDx value. Of course, that is valid only for cases where micro timer modulus down-counter produces 1us time base.

So, for your cases:

Case1. PITLD0 = 1000 -> 1001us

Case2. PTILD0 = 999 -> 1000us

I hope it helps you.

Have a great day,

RadekS

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------