- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Emulating I2S bus on Kinetis-EA

Emulating I2S bus on Kinetis-EA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I found an application note(AN4944) that emulating I2S bus on Kinetis-M with minimal CPU load.

But my design now is using KEAZ series without DMA and timer counter.

It looks like CPU will have limit performance while play audio sound.

Is there anyone have any idea can share with me?

Thanks.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kyle,

I haven't ported the AN4944 to KEA series MCU before.

I think it will burden the core a lot with emulating I2S without using DMA , how about choose another MCU which integrates with the DMA module instead of the KEA?

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here's the solution, code is attached.

IAR project file: build\iar\ke06\SPI_MasterInt_demo\SPI_MasterInt_demo.eww

HW/SW Requirement

Hardware

- FRDM-KE06Z (RevA)

- TWR-AUDIO-SGTL (RevF)

Software

- IAR 7.40.x

- Demo source code package (include KE06 driver lib)

Hardware Configuration

Connections between two boards

Pin function | FRDM-KE06Z | TWR-AUDIO-SGTL |

I2C SDA | PTA2 (J2-18) | ELEV_I2C0_SDA (PRIMARY A8) |

I2C SCL | PTA3 (J2-20) | ELEV_I2C0_SCL (PRIMARY A7) |

I2S BCLK | PTB2 (J2-12) | ELEV_I2S0_SCLK (PRIMARY A22) |

I2S TX FS | PTC5 (J1-11) | ELEV_I2S0_LRCLK (PRIMARY A23) |

I2S TXD | PTB3 (J2-8) | ELEV_I2S0_DIN (PRIMARY A25) |

GND | GND (J2-14) | GND (PRIMARY A26) |

FRDM-KE06Z

To generate Frame Sync signal for I2S by using FTM, the SPI SCK (BCLK) must be used as FTM clock source, connected to TCLK1:

PTB2 (J2-12) <-> PTE0 (J4-1)

TWR-AUDIO-SGTL

Power from the ELEVATOR 5V: J5 set.

MCLK is in from onboard 24.576MHz crystal: J6 unset.

Headphone is inserted to J7.

Software Configuration

Simulated I2S

- I2S Sample rate – 12KHz

- I2S format – S16_LE (left justified)

- I2S Bit Rate – 32x12KHz=384KHz

SPI

- SPI0 SCK as I2S BCLK – Baud Rate 384Khz

- SPI0 MOSI as I2S TXD

- Polling mode

FTM

- FTM1 as EPWM mode, clock source is external from SPI0 SCK

- FTM1 C1V=16, MOD=31

- FTM1 CH1 output as I2S TX_FS – 12KHz

I2C

- I2C0 SDA/SCL access the SGTL5000

Software Workaround

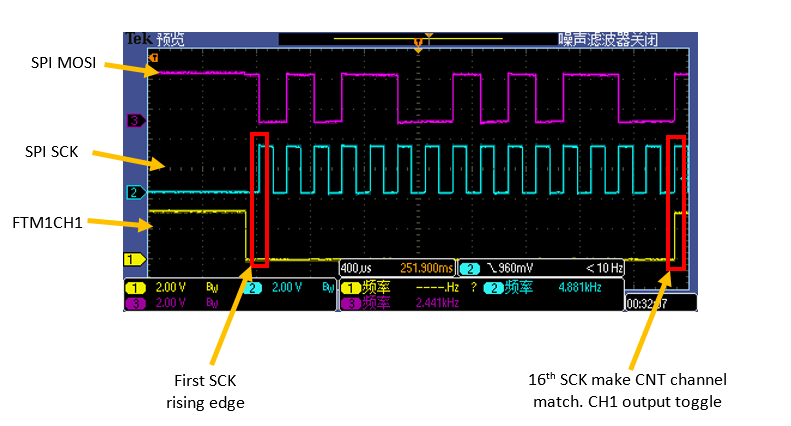

To use the SPI SCK as external clock source for FTM EPWM counter, there is a limitation: the FTM counter is increased on the rising edge of external clock, so the channel match and overflow event (FTM1CH1 output toggle) would happen on the rising edge of the external clock. Due to this, the data on the SPI MOSI must be valid on the SCK falling edge to make sure the data would not be fetched on the edge of frame sync. This causes the first left channel frame sync (TX_FS) would be one BCLK ahead of I2S data. This first left channel only contains 15bits valid data, see below figure:

A software workaround must be made to drop the 8th bit in the first 8bit data, to make sure all of the other data left and TX_FS is synced.

SPI_WriteDataReg(SPI0, (music[0] << 1) | ((music[1] >> 7) & 0x01));

/* start to transfer to send and receive date in non-block mode */

For (i = 1; i < MUSIC_LEN - 1; i++)

{

while(!SPI_IsSPTEF(SPI0));

SPI_WriteDataReg(SPI0, (music[i] << 1) | (music[i+1] >> 7));

}

Other Considerations

The general I2S frame rate is 12K/32K/44.1K/48K/96K, bit length is 16/24/32. So the BCLK frequency is frame_rate x 16, 24 or 32. For I2S clocking, a 32.768 KHz, 12.288 MHz or 24.576 MHz clock is recommend to generate the BCLK/FSCLK.

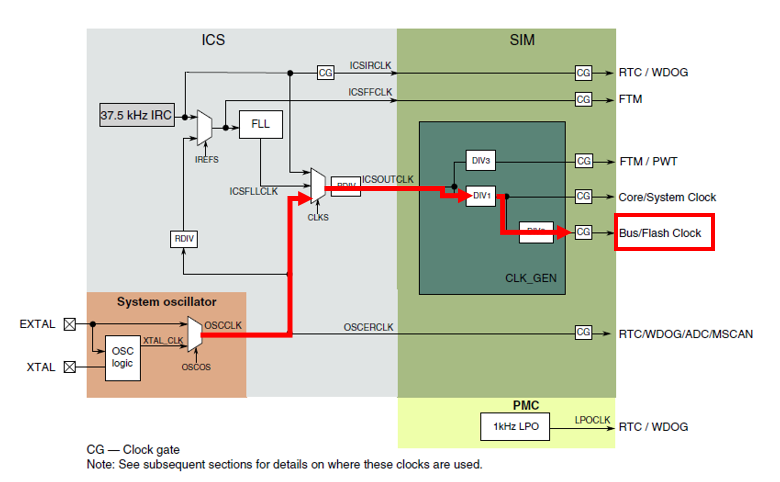

You cannot get a very accuracy BCLK from SPI SCK by using the internal IRC or connected a normal external crystal like 8MHz, 12MHz. The SPI clock source is from BUS_CLK, and no fractional divider supported. So to get an accuracy sample rate, a 12.288MHz, 24.576MHz is recommend to connect to EXTAL/XTAL for the BCLK/FSCLK generation. The FLL bypassed external (FBE) clock mode is selected with FLL disabled.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xinyu Chen

The current audio sample rate is 12kHz, is it have chance to increase to 44.1kHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kyle

For HW change: see the "Other Considerations" above.

For SW change:

- You need to change the following macro in SPI_MasterInt_demo.c to 44100

#define SAMPLE_RATE 12000

- Also configure the system/core/bus clock from external OSC, but not IRC.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xinyu Chen

Thanks for your help.

I will try it and give you a reply.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kyle

Please identify what sample rate, and bit format need for customers' requirement?

Also what's the CPU loading requirement?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xinyu Chen

Regarding the information of sample rate is 44.1kHz and bit format is 16-bit.

MCU is doing simple data bypass function from touch panel input via I2C interface and transfer through CAN bus to CPU.

Thanks for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kyle,

To implement the AN4944, you should guarantee the precision of the audio samples at first.

The Kinetis M series MCU is applicable to metering and measurement application which has a high accuracy Sigma-Delta ADC.

However the KEA series MCU doesn't have the high accuracy Sigma-Delta ADC and DMA module neither.

So I'd highly recommend that you should use the Kinetis M series instead of the KEA series MCU.

Hope it helps.

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy

My application is only emulating I2S bus on KEAZ series without audio stereo input, so no need high accuracy Sigma-Delta ADC.

KEAZ only send I2S data to codec while some function are active.

Do you have any experience regarding emulating I2S on KEAZ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kyle,

I haven't ported the AN4944 to KEA series MCU before.

I think it will burden the core a lot with emulating I2S without using DMA , how about choose another MCU which integrates with the DMA module instead of the KEA?

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeremy

Thanks for your comment.

If any new update, please shared with me.

Thanks.