- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- PGA for MC9S12ZVL

PGA for MC9S12ZVL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

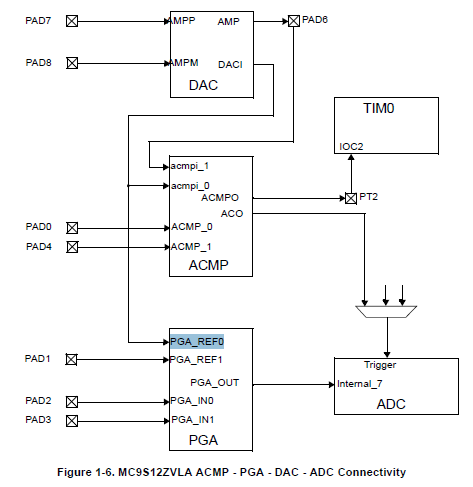

Regarding to PGA concept, I have 2 analog signals output from the Low Pass Filter Circuits . These 2 signals are then fed into the microcontroller MC9S12ZVLA as the PGA circuit inputs.

Following are the Register configurations done

PGAEN = 1;

PGAGAIN = 0x02; /* 40x*/

PGAOFFSET = 0x00; /*Disabled OFFSET*/

/* ==== Analog Mode Operation for HVI pin (IGN_FB). ==== */

PTAL_PTAENL = SET; /* 1 PL0 is connected to ADC */

PTAL_PTTEL = SET; /* Input buffer enabled when used with analog function */

PTAL_PTADIRL = CLEAR; /* Input voltage divider active on analog input to ADC channel */

PIRL_PIRL0 = 0x00; /* ratio selected 1:6 */

tPGA settling time given is 56us.

Vref of ADC is 5v.

When i sample first signal, its is getting Saturated to 0xFF (Higher than 2.6V) and other Saturated to 0x00 (Negative value less than 2.4V) .

Does anyone know if this could be a problem with the Mux or Settle timing tPGA? do you think we need more time?

Also,

I want to know How long does it take to sample the whole command sequence list to the ADC?

Thanks in advance

Charu

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Charudatta,

Unfortunately you mention here just half of PGA configuration.

Currently I do not see any connection between PGA and HVI configuration in your description.

Anyway, saturation for signal smaller than 2.4 and bigger than 2.6 look correct.

The output voltage for PGA_OUT as a function of PGAIN, PGAREF, gain and offset is calculated as follows:

VPGA_OUT = VPGAREF + APGA * (VPGAIN - VPGAREF + Voffset)

I suppose now that you use reference voltage 2.5V. If we will omit offset and fill the values, we will get:

VPGA_OUT= 2.5V+40*(2.4V-2.5V+0) = -1.5V

VPGA_OUT= 2.5V+40*(2.6V-2.5V+0) = 6.5V

These values are really out of 0V..5V range (saturation), despite on fact that sign don’t fit to your description.

The ADC works with some delays and latencies. For example:

“When the ADC is enabled the bits of ADCFLWCTL register can be modified after a latency time of three Bus Clock cycles.”

“Restart Mode: When the Restart Event has been processed (initial command of current CSL is loaded) it takes two Bus Clock cycles plus two ADC conversion clock cycles (pump phase) from the Trigger Event (bit TRIG set) until the select channel starts to sample.”

…

The sampling time is defined by SMP[4:0] bits in ADCCMD_2 (could be specified for every single command) and ADC clock. The whole ATD Conversion Period (for single ADC command) could be configured this way to 16-36 ADC clock cycles with 8 bit resolution or 18-38 ADC clock cycles with 10 bit resolution.

Of course, we have to sum all conversions (all commands) together for getting the whole command sequence list length.

Note: This simply sum suppose just one sequence of conversion commands in ADC command list.

I hope it helps you.

Have a great day,

RadekS

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Charudatta,

Unfortunately you mention here just half of PGA configuration.

Currently I do not see any connection between PGA and HVI configuration in your description.

Anyway, saturation for signal smaller than 2.4 and bigger than 2.6 look correct.

The output voltage for PGA_OUT as a function of PGAIN, PGAREF, gain and offset is calculated as follows:

VPGA_OUT = VPGAREF + APGA * (VPGAIN - VPGAREF + Voffset)

I suppose now that you use reference voltage 2.5V. If we will omit offset and fill the values, we will get:

VPGA_OUT= 2.5V+40*(2.4V-2.5V+0) = -1.5V

VPGA_OUT= 2.5V+40*(2.6V-2.5V+0) = 6.5V

These values are really out of 0V..5V range (saturation), despite on fact that sign don’t fit to your description.

The ADC works with some delays and latencies. For example:

“When the ADC is enabled the bits of ADCFLWCTL register can be modified after a latency time of three Bus Clock cycles.”

“Restart Mode: When the Restart Event has been processed (initial command of current CSL is loaded) it takes two Bus Clock cycles plus two ADC conversion clock cycles (pump phase) from the Trigger Event (bit TRIG set) until the select channel starts to sample.”

…

The sampling time is defined by SMP[4:0] bits in ADCCMD_2 (could be specified for every single command) and ADC clock. The whole ATD Conversion Period (for single ADC command) could be configured this way to 16-36 ADC clock cycles with 8 bit resolution or 18-38 ADC clock cycles with 10 bit resolution.

Of course, we have to sum all conversions (all commands) together for getting the whole command sequence list length.

Note: This simply sum suppose just one sequence of conversion commands in ADC command list.

I hope it helps you.

Have a great day,

RadekS

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a lot Radek,

Here Voffset is disabled .

So, as you anlaysed its getting saturated.

What I didn't get is the connection between PGA and HVI configuration.

Can you please guide me on this.

Our design is like this:

PGA shall be enabled in order to amplify Wheatstone Bridge terminals and take accurate samples from the pressure sensor by making

- PGAEN = 0x01 (EnablePGA, disable PGAOFFSCEN - 0 switch is off, no internal connection between PGAIN and PGAREF.)

- PGACNTL = 0x02 (Configure PGAINSEL to select PGA_IN0 and then PGA_IN1 with delay 0f 56us,

PGAREFSELset toVDDA/2)

- PGAGAIN = K_PGA_GAIN (0x02 = 40x)

- PGAOFFSET = 0 (Disable PGA Offset)

To get rid off this saturation? What PGAREF has to be configured ?

I could see options as

00 Internally generated VDDA / 2 is selected as reference voltage (PGAREF)

01 Reserved

10 External PGA_REF0 input is selected as reference voltage (PGAREF).

11 External PGA_REF1 input is selected as reference voltage (PGAREF).

Here what is meant by External PGA_REF0 and PGA_REF1?

Thanks and Regards

Charudatta

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Charudatta,

About “connection between PGA and HVI configuration”)

Your initial question contains this code:

/* ==== Analog Mode Operation for HVI pin (IGN_FB). ==== */

PTAL_PTAENL = SET; /* 1 PL0 is connected to ADC */

PTAL_PTTEL = SET; /* Input buffer enabled when used with analog function */

PTAL_PTADIRL = CLEAR; /* Input voltage divider active on analog input to ADC channel */

PIRL_PIRL0 = 0x00; /* ratio selected 1:6 */

About “To get rid off this saturation?”)

It is not question about reference but gain.

Your range 2.4V..2.6V = 0.2V multiplied by 40x is 8V, but range for ADC is just 0V..5V!

So, you couldn’t measure 2.4V..2.6V range with 40x gain despite on used reference.

Please use smaller gain - for example 20x.

About External PGA_REF0 and PGA_REF1)

I hope it helps you.

Have a great day,

RadekS

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------