- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- KL02 Port A No Control

KL02 Port A No Control

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am new the Kinetis world and I am having a head scratching problem.

I cannot seem to gain total control over the Port Control Registers for port A. I was having a problem setting the appropriate mux setting on individual pins then I learned I needed to enable the gate to clock the port which I did and that allowed me to set the mux functions on the pins. However, I also attempted to set the IRQC in the port control register (for some pin in port A) and will not work. Never sets the IRQC value. But the same construct works on any port B pin. I set the IRQC and the interrupt if enable is serviced. I check the SIM regs and both port A and B clocks are enabled. What is causing port A not to work?

I have scanned the documentation several times with nothing pointing me to a smoking gun.

Please help, seems like something simple but I cannot find it!

Many thanks,

B-rian

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Brian Petty:

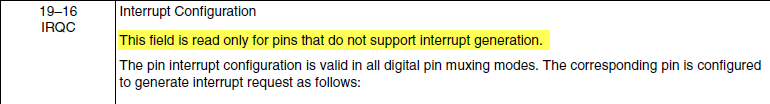

Some bits of the Port Control Register are read only if the pin does not support the corresponding feature. For example see the note for IRQC in the Reference Manual:

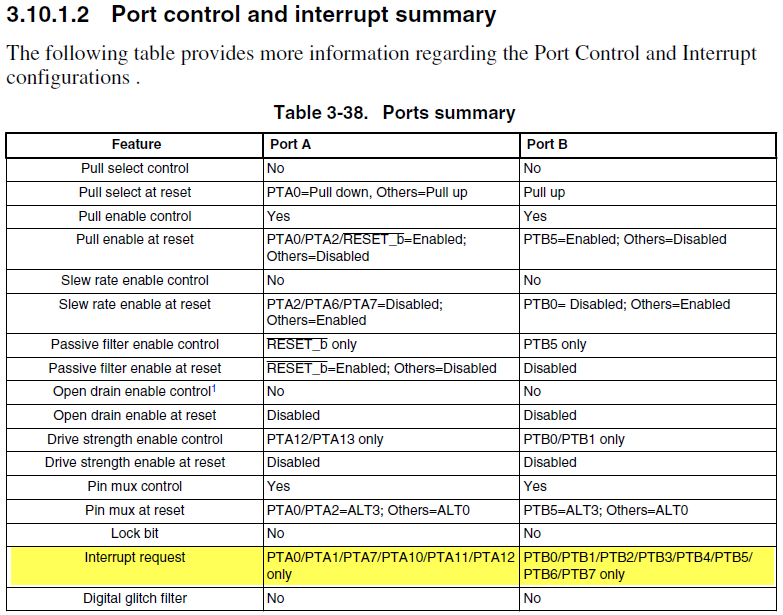

Then in the chapter Port Control and interrupt summary you can find this table:

You can see how PTA6 is not one of the pins supporting interrupts.

I hope this helps to clarify.

Best Regards!

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is my gpio_init function...

void gpio_init(void)

{

// enable clock for gpio ports a and b

SIM_SCGC5 |= SIM_SCGC5_PORTA_MASK + SIM_SCGC5_PORTB_MASK;

// select gpio as pin functionality

gpio_PTB_PCR1 |= PORT_PCR_MUX(PIN_FUNC_ALT1); // unused

gpio_PTB_PCR2 |= PORT_PCR_MUX(PIN_FUNC_ALT1); // adc_pdrst_n

gpio_PTB_PCR5 |= PORT_PCR_MUX(PIN_FUNC_ALT1); // unused

gpio_PTA_PCR6 |= PORT_PCR_MUX(PIN_FUNC_ALT1); // adc_drdy_n/spi_0_miso

// configure port b pins and clear output states of port b pins

gpio_PTB_PDDR |= gpio_PTB_PDRST_N + gpio_PTB_1_UNUSED + gpio_PTB_5_UNUSED;

gpio_PTB_PCOR |= gpio_PTB_PDRST_N + gpio_PTB_1_UNUSED + gpio_PTB_5_UNUSED;

// testing...

gpio_PTB_PCR2 |= PORT_PCR_IRQC(PIN_IRQC_8); -- this works...

gpio_PTA_PCR6 |= PORT_PCR_IRQC(PIN_IRQC_8); -- this does NOT! Why?

// configure port a pins

gpio_PTA_PDDR |= gpio_PTA_DRDY_N + gpio_PTA_5_UNUSED + gpio_PTA_7_UNUSED;

gpio_PTA_PCOR |= gpio_PTA_5_UNUSED + gpio_PTA_7_UNUSED;

return;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Brian Petty:

Some bits of the Port Control Register are read only if the pin does not support the corresponding feature. For example see the note for IRQC in the Reference Manual:

Then in the chapter Port Control and interrupt summary you can find this table:

You can see how PTA6 is not one of the pins supporting interrupts.

I hope this helps to clarify.

Best Regards!

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------