- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- Wait for PLL lock with S912XEG128J2MMA

Wait for PLL lock with S912XEG128J2MMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Wait for PLL lock with S912XEG128J2MMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have an issue that this wait time is very long ( 1 sec ~ 10min.) to exit this wait loop sometimes at out production line

- we found this issue only one time that the product have this issue. it is difficut to reproduce when this situation was found. almost could not reproduce,

- but,Some failure was found due to related this issue in the field,

we have assembled 100 product with S912XEG128J2MMA recently.

There are 3 product that have this issue

- 1 product takes 15 second to exit this loop only 1 time, could not reproduce after that.

- 2 product takes 15 min to exit this loop only 1 time, could not reproduce after that.

Could you advice me this issue?

the wait loop of the firmware is generated by Processor Expert of Codewarrior IDE, the loop is as follows

void _EntryPoint(void)

{

/* ### MC9S12XEG128_80 "Cpu" init code ... */

.................

while(CRGFLG_LOCK == 0U) { /* Wait until the PLL is within the desired tolerance of the target frequency */

}

/* CLKSEL: PLLSEL=1 */

setReg8Bits(CLKSEL, 0x80U); /* Select clock source from PLL */

/* VREGHTCL: ??=0,??=0,VSEL=0,VAE=1,HTEN=0,HTDS=0,HTIE=0,HTIF=0 */

setReg8(VREGHTCL, 0x10U);

/*** End of PE initialization code after reset ***/

/*lint -save -e950 Disable MISRA rule (1.1) checking. */

__asm("jmp _Startup"); /* Jump to C startup code */

/*lint -restore Enable MISRA rule (1.1) checking. */

}

#pragma CODE_SEG DEFAULT

/* END Cpu. */

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KWANGHO,

You are right, this time ( 1 sec ~ 10min.) is really too long.

There must be some issue in MCU clock.

Could you please share here schematic related to MCU clock (XTAL, EXTAL, XCLKS,…) and your clock settings (SYNR, REFDV, POSTDIV)?

External oscillator (crystal, resonator) is possible to connect by one of three possible options. See Figure 1-10., Figure 1-11. and Figure 1-12. In RM(page 88). XCLKS pin must be connected according this connection.

In attachment is PLL calculator for S12XE. You should just enter oscillator and bus frequency and see optimal values for SYNR, REFDV and POSTDIV registers.

Additionally I would like to recommend add loop for write into CLKSEL register – just for sure.

According RM: “It is recommended to read back the PLLSEL bit to make sure PLLCLK has really been selected as SYSCLK, as LOCK status bit could theoretically change at the very moment writing the PLLSEL bit.”

For example:

while(!CLKSEL_PLLSEL) // PLLSEL=1 check

{ while(!CRGFLG_LOCK); // Wait till the PLL VCO is within tolerance

CLKSEL_PLLSEL = 1; // Select clock source from PLLCLK

}

Instead of

while(CRGFLG_LOCK == 0U) { /* Wait until the PLL is within the desired tolerance of the target frequency */

}

/* CLKSEL: PLLSEL=1 */

setReg8Bits(CLKSEL, 0x80U); /* Select clock source from PLL */

I hope it helps you.

Have a great day,

RadekS

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Radek,

i work with Kwangho, Park in same company.

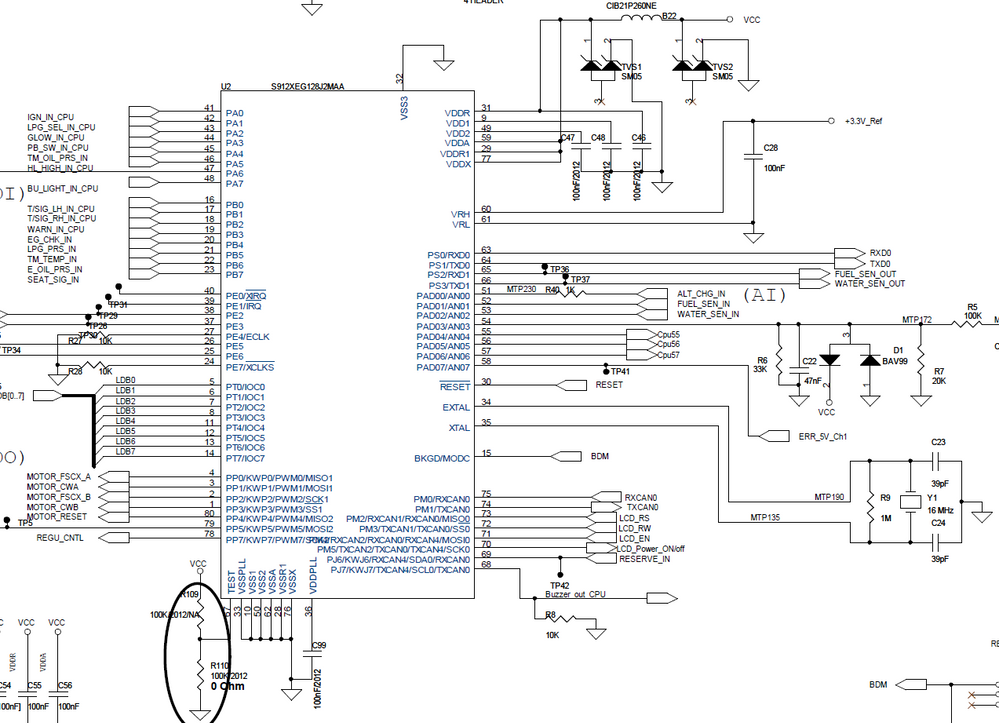

i attach the schematic and the clock settings which is generated by the Processor Expert.

your recommend is to modify the auto generated file by manually.

is it right ?

void _EntryPoint(void)

{

/*** !!! Here you can place your own code using property "User code before PE initialization" on the build options tab of the CPU compoennt. !!! ***/

/* ### MC9S12XEG128_80 "Cpu" init code ... */

/* PE initialization code after reset */

/* MMCCTL1: TGMRAMON=0,??=0,EEEIFRON=0,PGMIFRON=0,RAMHM=0,EROMON=0,ROMHM=0,ROMON=1 */

setReg8(MMCCTL1, 0x01U);

/* DIRECT: DP15=0,DP14=0,DP13=0,DP12=0,DP11=0,DP10=0,DP9=0,DP8=0 */

setReg8(DIRECT, 0x00U);

/* IVBR: IVB_ADDR=0xEF */

setReg8(IVBR, 0xEFU);

/* ECLKCTL: NECLK=0,NCLKX2=1,DIV16=0,EDIV4=0,EDIV3=0,EDIV2=0,EDIV1=0,EDIV0=0 */

setReg8(ECLKCTL, 0x40U);

/* System clock initialization */

/* CLKSEL: PLLSEL=0,PSTP=0,XCLKS=0,??=0,PLLWAI=0,??=0,RTIWAI=0,COPWAI=0 */

setReg8(CLKSEL, 0x00U); /* Select clock source from XTAL and set bits in CLKSEL reg. */

/* PLLCTL: CME=1,PLLON=0,FM1=0,FM0=0,FSTWKP=0,PRE=0,PCE=0,SCME=1 */

setReg8(PLLCTL, 0x81U); /* Disable the PLL */

/* SYNR: VCOFRQ1=0,VCOFRQ0=0,SYNDIV5=0,SYNDIV4=0,SYNDIV3=0,SYNDIV2=0,SYNDIV1=1,SYNDIV0=0 */

setReg8(SYNR, 0x02U); /* Set the multiplier register */

/* REFDV: REFFRQ1=1,REFFRQ0=0,REFDIV5=0,REFDIV4=0,REFDIV3=0,REFDIV2=0,REFDIV1=0,REFDIV0=1 */

setReg8(REFDV, 0x81U); /* Set the divider register */

/* POSTDIV: ??=0,??=0,??=0,POSTDIV4=0,POSTDIV3=0,POSTDIV2=0,POSTDIV1=0,POSTDIV0=0 */

setReg8(POSTDIV, 0x00U); /* Set the post divider register */

/* PLLCTL: CME=1,PLLON=1,FM1=0,FM0=0,FSTWKP=0,PRE=0,PCE=0,SCME=1 */

setReg8(PLLCTL, 0xC1U);

while(CRGFLG_LOCK == 0U) { /* Wait until the PLL is within the desired tolerance of the target frequency */

}

/* CLKSEL: PLLSEL=1 */

setReg8Bits(CLKSEL, 0x80U); /* Select clock source from PLL */

/* VREGHTCL: ??=0,??=0,VSEL=0,VAE=1,HTEN=0,HTDS=0,HTIE=0,HTIF=0 */

setReg8(VREGHTCL, 0x10U);

/*** End of PE initialization code after reset ***/

/*** !!! Here you can place your own code using property "User code after PE initialization" on the build options tab of the CPU component. !!! ***/

/*lint -save -e950 Disable MISRA rule (1.1) checking. */

__asm("jmp _Startup"); /* Jump to C startup code */

/*lint -restore Enable MISRA rule (1.1) checking. */

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi youngcheol,

Currently I do not see any obvious issue on you schematic.

Also PLL settings (generates bus clock 24MHz from 16MHz crystal clock) should work.

From my point of view:

1. 39pF capacitors (C23, C24) at crystal seem like quite big values. Typical values are rather around 10-20pF, however this depends also on crystal parameters. Could you please try smaller capacitances? Potentially you could consult it with crystal manufacturer.

2. I would like to recommend rather SYNR=0xC2, REFDV=0xC0, POSTDIV=0x01. Result frequency should be the same, just selected higher REFCLK is better for achieve optimum stability and shortest lock time. However personally I do not expect any significant improvements by this change.

Could you please check voltage levels at oscillator pins? The pins EXTAL, XTAL dedicated to the oscillator have a nominal 1.8 V level. They are supplied by VDDPLL.

You could also check your PCB layout.

These rules should be applied:

- VSSPLL must be directly connected to VSS3.

- Keep traces of VSSPLL, EXTAL, and XTAL as short as possible and occupied board area for C23, C24, R9 and Y1 as small as possible.

- Do not place other signals or supplies underneath area occupied by C23, C24, R9 and Y1 and the connection area to the MCU.

I hope it helps you.

Have a great day,

RadekS

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, Radek,

Thank you for your answer.

I will check the components, clock level and PCB Layout.

Also, I'll test with your recommend settings.

And i'll share the test result.

Best Regards,

Youngcheol Song