- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- T2081 PCIe problem

T2081 PCIe problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

T2081 PCIe problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

I am using the T2081 board made.

PCIex4 lanes of the T2081 has confirmed that the recognition by connecting to Altera FPGA.

* boot log

...

PCIe4: Root Complex, x4 gen1, regs @ 0xfe270000

01:00.0 - 1172:0004 - Does not fit any class

......

PCI host bridge /pcie@ffe270000 ranges:

MEM 0x0000000c40000000..0x0000000c4fffffff -> 0x00000000e0000000

IO 0x0000000ff8030000..0x0000000ff803ffff -> 0x0000000000000000

# lspci

00:00.0 Class 0604: 1957:0839

01:00.0 Class ff00: 1172:0004 <-- Altera FPGA

# cat /proc/iomem

00000000-ffffffff : System RAM

c40000000-c4fffffff : /pcie@ffe270000

c40000000-c4fffffff : PCI Bus 0000:01

c40000000-c400003ff : 0000:01:00.0

c40000400-c400007ff : 0000:01:00.0

c40000800-c40000bff : 0000:01:00.0

fe8000000-fefffffff : fe8000000.nor

........

Use the mmap64 receive an error as shown in Table 1, we read the 0xc40000000 address.

| Table 1 |

|---|

Machine check in kernel mode. Caused by (from MCSR=a000): Load Error Report Guarded Load Error Report Oops: Machine check, sig: 7 [#1] SMP NR_CPUS=24 CoreNet Generic Modules linked in: CPU: 0 PID: 1719 Comm: console_mmap Not tainted 3.12.37-rt51-QorIQ-SDK-V1.8+gf488de6 #7 task: c0000000e069d540 ti: c0000000e0e00000 task.ti: c0000000e0e00000 NIP: 0000000010000f88 LR: 0000000010000f58 CTR: c000000000306128 REGS: c0000000e0e03ea0 TRAP: 0000 Not tainted (3.12.37-rt51-QorIQ-SDK-V1.8+gf488de6) MSR: 000000000002f000 <CE,EE,PR,FP,ME> CR: 28000288 XER: 20000000 SOFTE: 1

GPR00: 0000000010000f58 00000000ffc7d2c0 00000000f7e7a4c0 0000000000000025 GPR04: 000000000fee0544 0000000000000000 0000000000004000 0000000010002185 GPR08: 0000000000000000 00000000f7e72000 00000000f7e72000 00000000ffc7d230 GPR12: 0000000044000222 000000001001a570 00000000100f0000 0000000000000000 GPR16: 0000000000000000 00000000100f46cc 00000000100f46bc 00000000100f0000 GPR20: 00000000100f48d8 0000000044444444 0000000000000000 000000001010f508 GPR24: 0000000000000000 000000001010f448 0000000000000000 00000000f7e76f18 GPR28: 00000000f7e77840 0000000000000000 000000000ffed344 00000000ffc7d2c0 NIP [0000000010000f88] 0x10000f88 LR [0000000010000f58] 0x10000f58 Call Trace: ---[ end trace 83d2ce4957171a6e ]---

[READ 10 BYTE DATA from 0x00000000] Bus error |

What's the problem?

If I may be so FPGA logic problem?

Attach the boot log.

Thank you.

Best regards,

gyosun.

Original Attachment has been moved to: t2081_boot.log.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I was getting a similar error when trying to write to a device in the PCIe window (read worked fine, but writes caused a crash). Turns out it was a programming error on my part. I was using the following, which was wrong:

int fd = open("/dev/mem", O_SYNC);

fpgaAddr = mmap(NULL, 0x100000, PROT_READ | PROT_WRITE, MAP_PRIVATE, fd, 0xc40000000);

When I corrected to this, everything worked fine:

int fd = open("/dev/mem", O_SYNC|O_RDWR);

fpgaAddr = mmap(NULL, 0x100000, PROT_READ | PROT_WRITE, MAP_SHARED, fd, 0xc40000000);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Machine check interrupt occurs (among other reasons) when the transaction

target does not respond. This may occur both because the target address

is invalid and because the target is not responding. Based on the

information in this post, it is not possible to determine what exactly

happens. The suggestions are:

1. Connect a good JTAG debugger to the system.

2. Step through your code, verify the parameters you pass to

mmap() and related calls. Make sure your code checks for errors

returned by mmap() befor using the pointer.

3. Try your code with a PCIe peripheral that is known working.

4. For hardware-level errors, immediately after machine check inspect registers

discussed in Sections 8.3.1.3 and 20.6.1.12 of the chip Reference Manual.

Have a great day,

Platon

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello bpe.

I'm having the same issue that gyosun is having. I'm getting the Machine Check exception when trying to read from PCIe4 I/O address space.

We have 2 custom CPU boards with QorIQ processors: one with the T2081 and another with the T1022. For the application we have a custom base board with the PCIe (x1 Gen2) link partner connected to SerDes lane E.

When using the T1022 CPU board I can communicate with the link partner normally. But with the T2081 I'm getting the Machine Check exception all the time.

The kernel driver for that is basically the same, with the difference that the T1022 runs in 32 bit mode and the T2081 in 64bit mode.

Please find attached the register's dump generated from the Corewarrior Debugger at the moment of the failure.

Could you please help me find out whats is wrong?

Thanks,

Tiago.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello again.

I found out what was the cause of my problems with PCIe4: I was using wrong memory ranges for PCIe device nodes on our board DTS file. After copying the memory ranges defined for the T2080RDB board the problem was solved.

Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Tiago,

Be glad to solve the problem. I 's still a problem.

What, and Where is the DTS?

How can you explain in detail that you solve the problem?

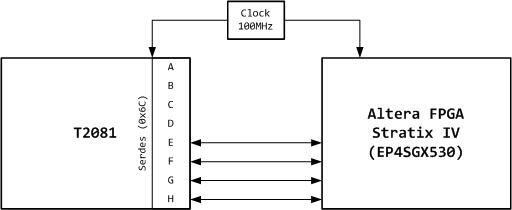

PCIe is connected to four lanes, as shown below.

Thanks,

Gyosun.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi bpe,

Thank you for answer.

Current structural JTAG hardware is unable to connect. No JTAG port.

CCSR register is well below the code. When you access the PCIE error.

int fd;

uint8_t *vaddr;

uint64_t baddr = 0xc40000000; // PCIe BAR0

//uint64_t baddr = 0xffe000000; // CCSR

fd = open("/dev/mem", O_RDWR | O_SYNC);

vaddr = (uint8_t *)mmap64(NULL, 0x400, PROT_READ | PROT_WRITE, MAP_SHARED, fd, baddr);

printf("%08x\r\n", *(uint32_t *)(vaddr));

close(fd);

When added to the PCIE no logic in the FPGA and stopped by reading the PCIE Register, when the PCIE logic is a kernel error message is output.

If you have any problems logic FPGA PCIE possible error occurs when using mmap?

I'm not sure what the problem. We need more help.

Best regards,

gyosun.