- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5674F core voltage generation and LVD

MPC5674F core voltage generation and LVD

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

the requirements concerning VDD generation and low voltage monitoring detection are still a little bit confusing and inconsistent in the current reference manual (Rev.7) and datasheet (Rev. 10.1).

Please help me to understand this topic by answering the following questions. I wanted to submit a Service Request, but it seems this is not possible anymore. Some questions seem to be very simple, but the documentation in older versions of the documentation is completely different.

question 1: Do you confirm, that for exiting the reset state the internally or externally generated core voltage needs to be higher than V_LVD12 x (1 + 6%) = 1.166V after power-up? This would mean that the 1.14V specified in datasheet table 14 (spec line 1) are not sufficient during power-up.

question 2: Do you confirm, that when the µC has left the reset state an internally or externally generated core voltage of 1.08V is sufficient (in case low voltage monitoring is disabled) and does not lead to any performance degradation? Refer to datasheet table 14 spec line 1a.

question 3: Do you confirm, that the reset value of PMC_TRIMR[VDDCTRIM] is 0000 and that this setting corresponds to nominal V_DD12OUT = 1.27V?

question 4: Do you confirm, that when internal regulator is used, PMC_TRIMR[VDDCTRIM] shall be set to 1100 and that this setting corresponds to nominal 1.23V?

question 5: Do you confirm, that the reset value of PMC_TRIMR[LVDCTRIM] is 1010 and corresponds to nominal V_LVD12 = 1.10V?

question 6: Do you confirm, that the PMC_TRIMR[LVDCTRIM] shall be set to 0110 (according to reference manual table 4-5) and that this setting corresponds to nominal 1.22V? (Would be unlikely.)

question 7: Do you confirm, that the PMC_TRIMR[LVDCTRIM] shall be set to 1100 (according to reference manual text of chapter 4.5.7) and that this setting corresponds to nominal 1.12V?

question 8: Do you confirm, that for the correct setting of PMC_TRIMR[LVDCTRIM] it is not relevant whether the VDD is generated internally or externally?

Thank you in advance.

Matthias

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

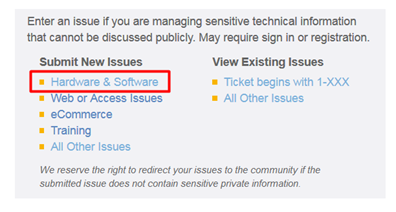

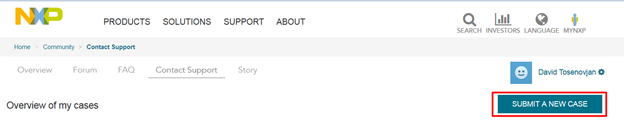

You still can submit service request, but it is called “case” and you will find it under SALES AND SUPPORT:

Then you will have to sign in or register with new user account and password and then you can submit new case over following screen:

If you don’t want to discuss it publicly, submit new case (i.e. ticket/service request/issue).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You still can submit service request, but it is called “case” and you will find it under SALES AND SUPPORT:

Then you will have to sign in or register with new user account and password and then you can submit new case over following screen:

If you don’t want to discuss it publicly, submit new case (i.e. ticket/service request/issue).