- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Design Studio

- :

- SPI Chip select and configuration

SPI Chip select and configuration

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

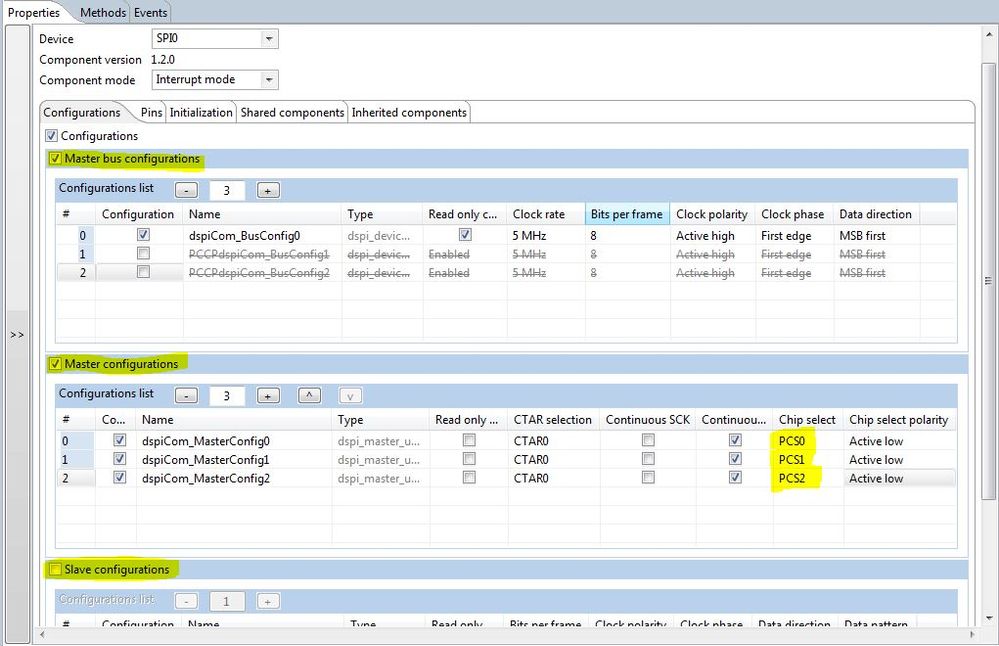

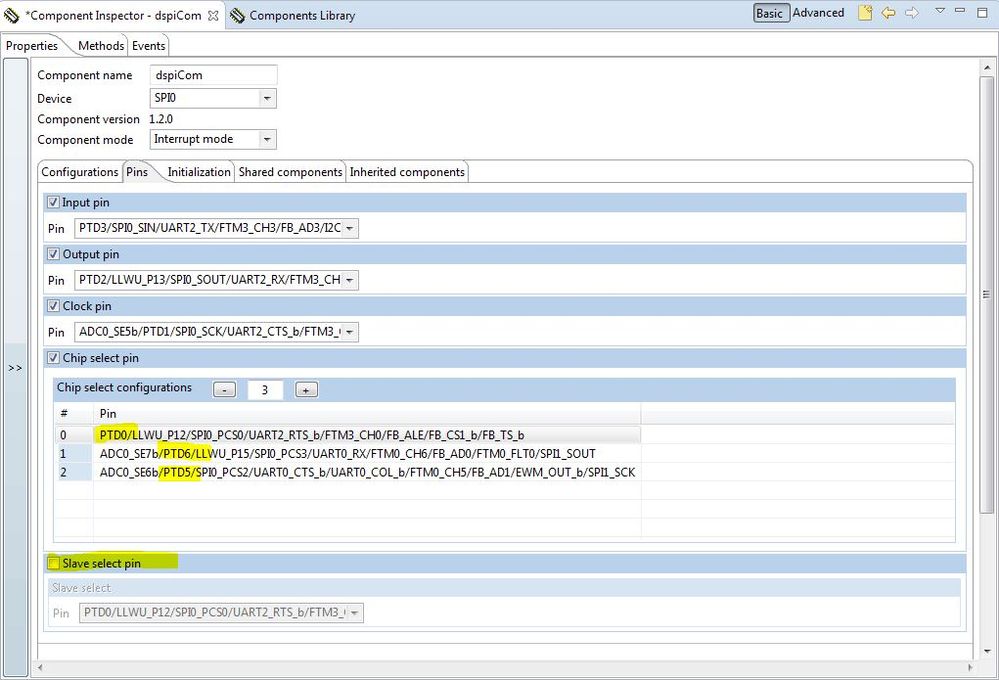

I have an SPI master(K64) configured with below settings. Currently, I am able to communicate only with one of the slave connected on Chip select pin PTD6. I am not doing anything through code apart from setdelay between CS and Clock. So is there anything else which needs to be configured.

How does the HAL know which pin chip selects to, if its PTD5,6,0

In the HAL layer, all I could see was

/*! @brief DSPI Peripheral Chip Select (PCS) configuration (which PCS to configure)*/

typedef enum _dspi_which_pcs_config {

kDspiPcs0 = 1 << 0, /*!< PCS[0] @internal gui name="PCS0" */

kDspiPcs1 = 1 << 1, /*!< PCS[1] @internal gui name="PCS1" */

kDspiPcs2 = 1 << 2, /*!< PCS[2] @internal gui name="PCS2" */

kDspiPcs3 = 1 << 3, /*!< PCS[3] @internal gui name="PCS3" */

kDspiPcs4 = 1 << 4, /*!< PCS[4] @internal gui name="PCS4" */

kDspiPcs5 = 1 << 5 /*!< PCS[5] @internal gui name="PCS5" */

} dspi_which_pcs_config_t;

I think its a potential bug here in KDS.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Alice,

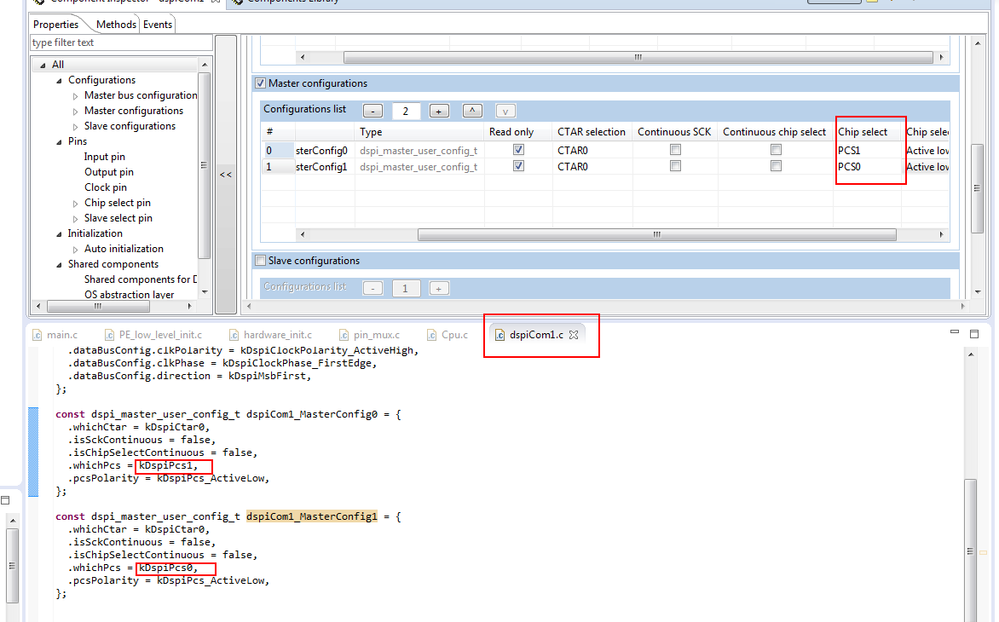

I guess I am wrong, In the first screen shot attached I have selected the PCS0,1,2 however in the chip select configurations I have selected the SPI0_PCS0, 2 and 3. but not SPI0_PCS1.

My slaves devices are connected on SPI0_PCS0, SPI0_PC2, SPI0_PCS3 so I should be selecteding the Masterconfig with PCS0, PCS2, PCS3 right.

so by doing that and what you suggested doing an external init I am able to get a response from PCS2 and PCS3. but failed to get any response from PCS0 however, the PCS0 enable is going low. So is it that the MISO line is held low/ high impedance state by any other devices.

I am doing an external SPI Initialize using code below just before sending the first packet.

void InitializeSPI( void )

{

// /* SIM_SCGC6: SPI0=1 */

// SIM_SCGC6 |= SIM_SCGC6_SPI0_MASK;

// /* Interrupt vector(s) priority setting */

//// /* NVICIP26: PRI26=0x70 */

//// NVICIP26 = NVIC_IP_PRI26(0x70);

//// /* NVICISER0: SETENA|=0x04000000 */

//// NVICISER0 |= NVIC_ISER_SETENA(0x04000000);

// /* SIM_SCGC5: PORTD=1 */

// SIM_SCGC5 |= SIM_SCGC5_PORTD_MASK;

// /* PORTD_PCR3: ISF=0,MUX=2 */

// PORTD_PCR3 = (uint32_t)((PORTD_PCR3 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR2: ISF=0,MUX=2 */

// PORTD_PCR2 = (uint32_t)((PORTD_PCR2 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR1: ISF=0,MUX=2 */

// PORTD_PCR1 = (uint32_t)((PORTD_PCR1 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR4: ISF=0,MUX=2 */

// PORTD_PCR4 = (uint32_t)((PORTD_PCR4 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR5: ISF=0,MUX=2 */

// PORTD_PCR5 = (uint32_t)((PORTD_PCR5 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR0: ISF=0,MUX=2 */

// PORTD_PCR0 = (uint32_t)((PORTD_PCR0 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR6: ISF=0,MUX=2 */

// PORTD_PCR6 = (uint32_t)((PORTD_PCR6 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

/* SPI0_MCR: MSTR=0,CONT_SCKE=0,DCONF=0,FRZ=0,MTFE=0,PCSSE=0,ROOE=1,??=0,??=0,PCSIS=0x0F,DOZE=0,MDIS=0,DIS_TXF=0,DIS_RXF=0,CLR_TXF=0,CLR_RXF=0,SMPL_PT=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,HALT=1 */

SPI0_MCR = SPI_MCR_DCONF(0x00) |

SPI_MCR_ROOE_MASK |

SPI_MCR_PCSIS(0x0F) |

SPI_MCR_SMPL_PT(0x00) |

SPI_MCR_HALT_MASK; /* Set Configuration register */

/* SPI0_MCR: MSTR=1,CONT_SCKE=0,DCONF=0,FRZ=0,MTFE=0,PCSSE=0,ROOE=1,??=0,??=0,PCSIS=0x0F,DOZE=0,MDIS=0,DIS_TXF=1,DIS_RXF=1,CLR_TXF=1,CLR_RXF=1,SMPL_PT=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,HALT=1 */

SPI0_MCR = SPI_MCR_MSTR_MASK |

SPI_MCR_DCONF(0x00) |

SPI_MCR_ROOE_MASK |

SPI_MCR_PCSIS(0x0F) |

SPI_MCR_DIS_TXF_MASK |

SPI_MCR_DIS_RXF_MASK |

SPI_MCR_CLR_TXF_MASK |

SPI_MCR_CLR_RXF_MASK |

SPI_MCR_SMPL_PT(0x00) |

SPI_MCR_HALT_MASK; /* Set Configuration register */

/* SPI0_CTAR0: DBR=1,FMSZ=0x0F,CPOL=0,CPHA=0,LSBFE=0,PCSSCK=3,PASC=3,PDT=3,PBR=2,CSSCK=1,ASC=1,DT=1,BR=1 */

SPI0_CTAR0 = SPI_CTAR_DBR_MASK |

SPI_CTAR_FMSZ(0x07) |

SPI_CTAR_PCSSCK(0x03) |

SPI_CTAR_PASC(0x03) |

SPI_CTAR_PDT(0x03) |

SPI_CTAR_PBR(0x02) |

SPI_CTAR_CSSCK(0x01) |

SPI_CTAR_ASC(0x01) |

SPI_CTAR_DT(0x01) |

SPI_CTAR_BR(0x01); /* Set Clock and Transfer Attributes register */

/* SPI0_SR: TCF=1,TXRXS=0,??=0,EOQF=1,TFUF=1,??=0,TFFF=1,??=0,??=0,??=0,??=1,??=0,RFOF=1,??=0,RFDF=1,??=0,TXCTR=0,TXNXTPTR=0,RXCTR=0,POPNXTPTR=0 */

SPI0_SR = SPI_SR_TCF_MASK |

SPI_SR_EOQF_MASK |

SPI_SR_TFUF_MASK |

SPI_SR_TFFF_MASK |

SPI_SR_RFOF_MASK |

SPI_SR_RFDF_MASK |

SPI_SR_TXCTR(0x00) |

SPI_SR_TXNXTPTR(0x00) |

SPI_SR_RXCTR(0x00) |

SPI_SR_POPNXTPTR(0x00) |

0x00200000U; /* Clear flags */

/* SPI0_RSER: TCF_RE=0,??=0,??=0,EOQF_RE=0,TFUF_RE=0,??=0,TFFF_RE=0,TFFF_DIRS=0,??=0,??=0,??=0,??=0,RFOF_RE=0,??=0,RFDF_RE=1,RFDF_DIRS=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SPI0_RSER = SPI_RSER_RFDF_RE_MASK; /* Set DMA Interrupt Request Select and Enable register */

/* SPI0_MCR: HALT=0 */

SPI0_MCR &= (uint32_t)~(uint32_t)(SPI_MCR_HALT_MASK);

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kewal,

Your configuration is right.

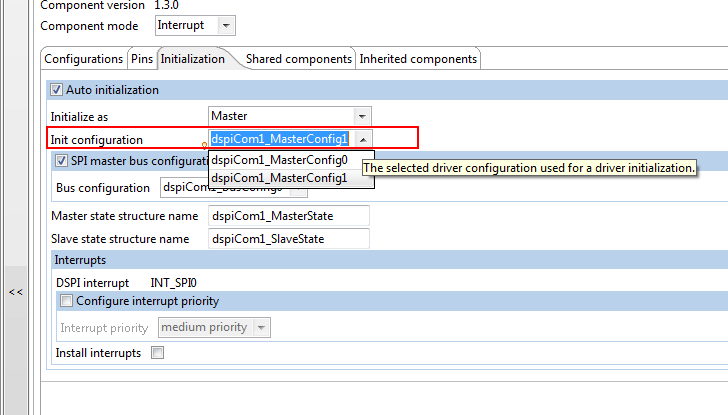

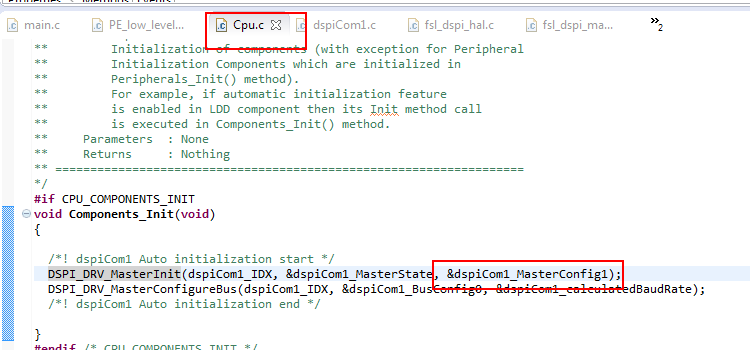

- And about which chip select to , after we configured the "chip select ", we can see the generate code on the file of"dspiCom1.c",

not on the HAL file .

- The reason why only one slave spi work is that, in the Auto initialization code ,it can only select one of them to initialize.

so when you want select the other two slave SPI ,you can initialize them by hand refer to the code under "comopnents_init".

or i think you can also use this function :

DSPI_HAL_SetPcsPolarityMode(base, userConfig->whichPcs, userConfig->pcsPolarity);

Hope it helps

Have a great day,

Alice Yang

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Alice,

I guess I am wrong, In the first screen shot attached I have selected the PCS0,1,2 however in the chip select configurations I have selected the SPI0_PCS0, 2 and 3. but not SPI0_PCS1.

My slaves devices are connected on SPI0_PCS0, SPI0_PC2, SPI0_PCS3 so I should be selecteding the Masterconfig with PCS0, PCS2, PCS3 right.

so by doing that and what you suggested doing an external init I am able to get a response from PCS2 and PCS3. but failed to get any response from PCS0 however, the PCS0 enable is going low. So is it that the MISO line is held low/ high impedance state by any other devices.

I am doing an external SPI Initialize using code below just before sending the first packet.

void InitializeSPI( void )

{

// /* SIM_SCGC6: SPI0=1 */

// SIM_SCGC6 |= SIM_SCGC6_SPI0_MASK;

// /* Interrupt vector(s) priority setting */

//// /* NVICIP26: PRI26=0x70 */

//// NVICIP26 = NVIC_IP_PRI26(0x70);

//// /* NVICISER0: SETENA|=0x04000000 */

//// NVICISER0 |= NVIC_ISER_SETENA(0x04000000);

// /* SIM_SCGC5: PORTD=1 */

// SIM_SCGC5 |= SIM_SCGC5_PORTD_MASK;

// /* PORTD_PCR3: ISF=0,MUX=2 */

// PORTD_PCR3 = (uint32_t)((PORTD_PCR3 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR2: ISF=0,MUX=2 */

// PORTD_PCR2 = (uint32_t)((PORTD_PCR2 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR1: ISF=0,MUX=2 */

// PORTD_PCR1 = (uint32_t)((PORTD_PCR1 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR4: ISF=0,MUX=2 */

// PORTD_PCR4 = (uint32_t)((PORTD_PCR4 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR5: ISF=0,MUX=2 */

// PORTD_PCR5 = (uint32_t)((PORTD_PCR5 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR0: ISF=0,MUX=2 */

// PORTD_PCR0 = (uint32_t)((PORTD_PCR0 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

// /* PORTD_PCR6: ISF=0,MUX=2 */

// PORTD_PCR6 = (uint32_t)((PORTD_PCR6 & (uint32_t)~(uint32_t)(

// PORT_PCR_ISF_MASK |

// PORT_PCR_MUX(0x05)

// )) | (uint32_t)(

// PORT_PCR_MUX(0x02)

// ));

/* SPI0_MCR: MSTR=0,CONT_SCKE=0,DCONF=0,FRZ=0,MTFE=0,PCSSE=0,ROOE=1,??=0,??=0,PCSIS=0x0F,DOZE=0,MDIS=0,DIS_TXF=0,DIS_RXF=0,CLR_TXF=0,CLR_RXF=0,SMPL_PT=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,HALT=1 */

SPI0_MCR = SPI_MCR_DCONF(0x00) |

SPI_MCR_ROOE_MASK |

SPI_MCR_PCSIS(0x0F) |

SPI_MCR_SMPL_PT(0x00) |

SPI_MCR_HALT_MASK; /* Set Configuration register */

/* SPI0_MCR: MSTR=1,CONT_SCKE=0,DCONF=0,FRZ=0,MTFE=0,PCSSE=0,ROOE=1,??=0,??=0,PCSIS=0x0F,DOZE=0,MDIS=0,DIS_TXF=1,DIS_RXF=1,CLR_TXF=1,CLR_RXF=1,SMPL_PT=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,HALT=1 */

SPI0_MCR = SPI_MCR_MSTR_MASK |

SPI_MCR_DCONF(0x00) |

SPI_MCR_ROOE_MASK |

SPI_MCR_PCSIS(0x0F) |

SPI_MCR_DIS_TXF_MASK |

SPI_MCR_DIS_RXF_MASK |

SPI_MCR_CLR_TXF_MASK |

SPI_MCR_CLR_RXF_MASK |

SPI_MCR_SMPL_PT(0x00) |

SPI_MCR_HALT_MASK; /* Set Configuration register */

/* SPI0_CTAR0: DBR=1,FMSZ=0x0F,CPOL=0,CPHA=0,LSBFE=0,PCSSCK=3,PASC=3,PDT=3,PBR=2,CSSCK=1,ASC=1,DT=1,BR=1 */

SPI0_CTAR0 = SPI_CTAR_DBR_MASK |

SPI_CTAR_FMSZ(0x07) |

SPI_CTAR_PCSSCK(0x03) |

SPI_CTAR_PASC(0x03) |

SPI_CTAR_PDT(0x03) |

SPI_CTAR_PBR(0x02) |

SPI_CTAR_CSSCK(0x01) |

SPI_CTAR_ASC(0x01) |

SPI_CTAR_DT(0x01) |

SPI_CTAR_BR(0x01); /* Set Clock and Transfer Attributes register */

/* SPI0_SR: TCF=1,TXRXS=0,??=0,EOQF=1,TFUF=1,??=0,TFFF=1,??=0,??=0,??=0,??=1,??=0,RFOF=1,??=0,RFDF=1,??=0,TXCTR=0,TXNXTPTR=0,RXCTR=0,POPNXTPTR=0 */

SPI0_SR = SPI_SR_TCF_MASK |

SPI_SR_EOQF_MASK |

SPI_SR_TFUF_MASK |

SPI_SR_TFFF_MASK |

SPI_SR_RFOF_MASK |

SPI_SR_RFDF_MASK |

SPI_SR_TXCTR(0x00) |

SPI_SR_TXNXTPTR(0x00) |

SPI_SR_RXCTR(0x00) |

SPI_SR_POPNXTPTR(0x00) |

0x00200000U; /* Clear flags */

/* SPI0_RSER: TCF_RE=0,??=0,??=0,EOQF_RE=0,TFUF_RE=0,??=0,TFFF_RE=0,TFFF_DIRS=0,??=0,??=0,??=0,??=0,RFOF_RE=0,??=0,RFDF_RE=1,RFDF_DIRS=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SPI0_RSER = SPI_RSER_RFDF_RE_MASK; /* Set DMA Interrupt Request Select and Enable register */

/* SPI0_MCR: HALT=0 */

SPI0_MCR &= (uint32_t)~(uint32_t)(SPI_MCR_HALT_MASK);

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kewal,

I think you should first be sure whether the slave0 (connected to the PCS0) send reply.

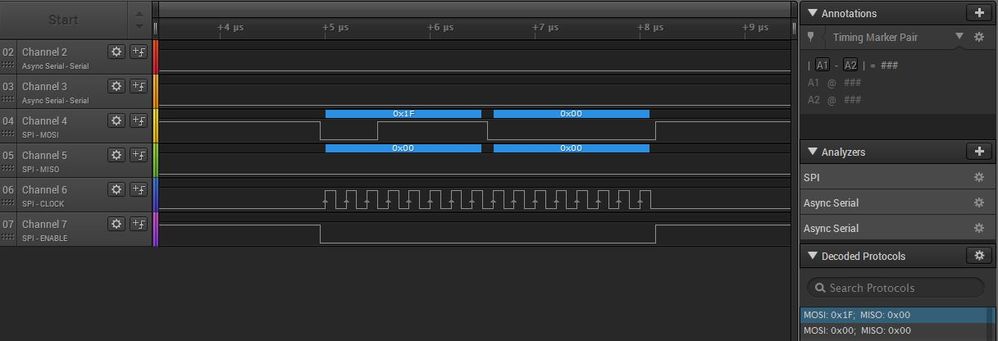

From your screenshot we can see the M0SI work well , while the MISO have no data ,

so maybe the slave do not work well .

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Alice,

I have got it working now and the reason was the reset pin on the slave was tied to low,.. :smileysad:

Anwyays, since you earlier said

so when you want select the other two slave SPI ,you can initialize them by hand refer to the code under "comopnents_init".

or i think you can also use this function :

DSPI_HAL_SetPcsPolarityMode(base, userConfig->whichPcs, userConfig->pcsPolarity);

so I was wondering how to actually switch between slaves.

//Always consider camera instance

DSPI_DRV_MasterDeinit(FSL_PCCPDSPICOM);

DSPI_DRV_MasterInit(FSL_PCCPDSPICOM, &PCCPdspiCom_MasterState, &PCCPdspiCom_MasterConfig0);

//Always consider camera instance

DSPI_DRV_MasterDeinit(FSL_PCCPDSPICOM);

DSPI_DRV_MasterInit(FSL_PCCPDSPICOM, &PCCPdspiCom_MasterState, &PCCPdspiCom_MasterConfig1);