- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- Digital Signal Controllers

- :

- frequency settings influence the ADC result

frequency settings influence the ADC result

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

frequency settings influence the ADC result

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i have a MC56F84769 controller. My bus clock is 50Mhz.

In the register ADC16_CFG1 I can select the clock divide settings (see below). The data sheet specifies that I need for 12Bit mode to keep inside 1.0 — 18.0Mhz.

If I change the divider settings between 4 and 8 during conversion my result changes although I am within the specified frequency.

Any ideas?

(00 The divide ratio is 1 and the clock rate is input clock.

01 The divide ratio is 2 and the clock rate is (input clock)/2.

10 The divide ratio is 4 and the clock rate is (input clock)/4.

11 The divide ratio is 8 and the clock rate is (input clock)/8.)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Andreas,

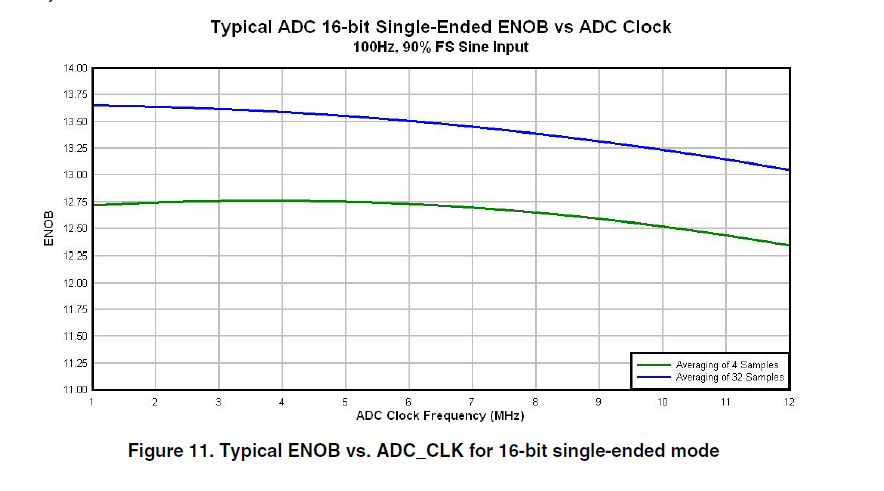

As the following Fig in data sheet of MC56F847xx, the higher the ADC clock frequency, the less the ENOB spec, accordingly more the noise is. For high accuracy, pls decrease the ADC clock frequency to 1MHz.

Hope it can help you.

BR

Xiangjun Rong