- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Controlling a RGB led with PWM on frdm-k64f

Controlling a RGB led with PWM on frdm-k64f

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have the frdm-k64f and the mbed application shield. On this shield there is a RGB led that I'm trying to control. However nothin happens. It looks like no pules is generated at all.

static inline void RGB_LED(uint32_t red, uint32_t green, uint32_t blue) {

//FTM0_C5V = red;

FTM0_C4V = green;

FTM0_C7V = blue;

}

void frdm_as_led_init() {

// Power on

SIM_SCGC5 |= SIM_SCGC5_PORTC_MASK | SIM_SCGC5_PORTA_MASK;

SIM_SCGC6 |= SIM_SCGC6_FTM0_MASK;

//SIM_SOPT4 |= SIM_SOPT4_FTM0TRG0SRC(1);

//NOTE: multiplexing port pat0 will cause cpu to hard fault on revision other then E

// because it's also routed to the debugger

//PORTA_PCR0 = PORT_PCR_MUX(3); // FTM0_CH5

PORTC_PCR4 = PORT_PCR_MUX(4); // FTM0_CH4

PORTA_PCR2 = PORT_PCR_MUX(3); // FTM0_CH7

RGB_LED(0,0,0);

// Make write_protected registers writable

FTM0_MODE |= FTM_MODE_WPDIS_MASK;

FTM0_MODE &= ~ FTM_MODE_FTMEN_MASK;

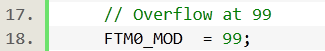

// Overflow at 99

FTM0_MOD = 99;

FTM0_CNTIN = 0;

FTM0_CNT = 0;

FTM0_C4SC = FTM_CnSC_MSB_MASK | FTM_CnSC_ELSA_MASK | FTM_CnSC_ELSB_MASK;

//FTM0_C5SC = FTM_CnSC_MSB_MASK | FTM_CnSC_ELSA_MASK;

FTM0_C7SC = FTM_CnSC_MSB_MASK | FTM_CnSC_ELSA_MASK | FTM_CnSC_ELSB_MASK;

FTM0_SC = FTM_SC_CLKS(1) | FTM_SC_PS(7); /* Edge Aligned PWM running from BUSCLK / 128 */

RGB_LED(400,400,400);

}

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

i think the CNT have not run up to 400 , when it up to 99, it overflow .

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alice,

Alice pointed out the root cause of the issue, and you can find the more information about the value of the CnV setting affects the duty cycle of the PWM pulse in the reference manual.

http://cache.nxp.com/files/microcontrollers/doc/ref_manual/K64P144M120SF5RM.pdf?fpsp=1&WT_TYPE=Refer...

Have a great day,

Ping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

i think the CNT have not run up to 400 , when it up to 99, it overflow .

Hope it helps

Alice