- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- iMX6DL : LVDS display pixel jitter

iMX6DL : LVDS display pixel jitter

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMX6DL : LVDS display pixel jitter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear community,

We face a problem.

We lower the i.MX6 core voltage , and

repeat the LVDS output switching(ON/OFF),then

a jitter occurs at the pixel on the LCD display.

Why will such a phenomenon occur on i.MX6 ?

The procedure to let a phenomenon reappear with a Sabre board are as follows.

[Reproduction Sequence]

Step1 : Change the core voltage to 1.175v at

arch/arm/mach-mx6/mx6q_sabresd_pmic_pfuze100.c

Step2 : Change the LDB Clock Source to PLL5 at

arch/arm/mach-mx6/clock.c

Step3 : Change the U-boot environment

Step4 : pour test2.rgb into fb0 in succession

Step5 : ON/OFF repeats the fb0 output switch by “blank command”

Then, a jitter occurs at a pixel.

The phenomenon occurs with porbability of 1/10 .

A loupe is necessary to confirm this phenomenon .

[System Configurations]

Board : MCIMX6DL-SDP

BSP : L3.0.35_4.1.0

[STEP1] Change the core voltage to 1.175v

arch/arm/mach-mx6/mx6q_sabresd_pmic_pfuze100.c

Line451

/*decrease VDDARM_IN/VDDSOC_IN,since we will use ldo bypass mode*/

/*VDDARM_IN 1.3V*/

ret = pfuze_reg_rmw(pfuze, PFUZE100_SW1AVOL,

PFUZE100_SW1AVOL_VSEL_M,

// 0x28); // 40d, 1.3V

0x23); // 35d, 1.175V

if (ret)

goto err;

/*VDDSOC_IN 1.3V*/

ret = pfuze_reg_rmw(pfuze, PFUZE100_SW1CVOL,

PFUZE100_SW1CVOL_VSEL_M,

// 0x28);

0x23); // 35d, 1.175V

[Step2] Change the LDB Clock Source to PLL5

arch/arm/mach-mx6/clock.c

static struct clk ldb_di0_clk = {

__INIT_CLK_DEBUG(ldb_di0_clk)

.id = 0,

// .parent = &pll2_pfd_352M,

.parent = &pll5_video_main_clk,

.enable_reg = MXC_CCM_CCGR3,

.enable_shift = MXC_CCM_CCGRx_CG6_OFFSET,

.enable = _clk_enable,

.disable = _clk_disable,

.set_parent = _clk_ldb_di0_set_parent,

.set_rate = _clk_ldb_di0_set_rate,

.round_rate = _clk_ldb_di_round_rate,

.get_rate = _clk_ldb_di0_get_rate,

.flags = AHB_HIGH_SET_POINT | CPU_FREQ_TRIG_UPDATE,

};

static struct clk ldb_di1_clk = {

__INIT_CLK_DEBUG(ldb_di1_clk)

.id = 0,

// .parent = &pll2_pfd_352M,

.parent = &pll5_video_main_clk,

.enable_reg = MXC_CCM_CCGR3,

.enable_shift = MXC_CCM_CCGRx_CG7_OFFSET,

.enable = _clk_enable,

.disable = _clk_disable,

.set_parent = _clk_ldb_di1_set_parent,

.set_rate = _clk_ldb_di1_set_rate,

.round_rate = _clk_ldb_di_round_rate,

.get_rate = _clk_ldb_di1_get_rate,

.flags = AHB_HIGH_SET_POINT | CPU_FREQ_TRIG_UPDATE,

};

//clk_set_parent(&ldb_di0_clk, &pll2_pfd_352M);

//clk_set_parent(&ldb_di1_clk, &pll2_pfd_352M);

clk_set_parent(&ldb_di0_clk, &pll5_video_main_clk);

clk_set_parent(&ldb_di1_clk, &pll5_video_main_clk);

[Step3] Change the U-boot environment

setenv loadaddr 0x10800000

setenv bootargs_base 'setenv bootargs console=ttymxc0,115200'

setenv bootargs_mmc 'setenv bootargs ${bootargs} root=/dev/mmcblk1p1 rootwait rw video=mxcfb0:dev=ldb,LDB-XGA,if=RGB666,ldb=dul1'

setenv bootcmd_mmc 'run bootargs_base bootargs_mmc;mmc dev 2;mmc read ${loadaddr} 0x800 0x2000;bootm'

setenv bootcmd 'run bootcmd_mmc'

saveenv

[Step4] pour test2.rgb into fb0 in succession

test2.sh is as follows.

#!/bin/sh

echo "test2.rgb"

while [ "1" ]

do

cat test2.rgb > /dev/fb0

done

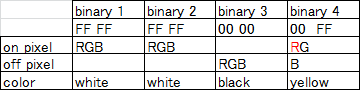

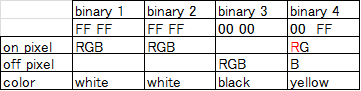

Test2.rgb format is

[ FF FF FF FF 00 00 00 FF] …… repeat

A jitter occurs at this Red pixel

I attach the input data file (test2.rgb).

[Step 5] ON/OFF repeats the fb0 output switch by “blank command”

sh test2.sh &

echo 1 > /sys/class/graphics/fb0/blank

echo 0 > /sys/class/graphics/fb0/blank

[Enter]

[Enter]

.......... repeat ............

Best Regards,

Koichi Sakagami

*************************************

Original Attachment has been moved to: test2.rgb.zip

Original Attachment has been moved to: test2.sh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As per the clock configuration the customer provided, they have switched the LDB root clock from the PLL2 PFD0 source, whose output frequency is 352MHz, to PLL5 output, whose output frequency is 630MHz. It seems to be too high, since the maximum serializer clock frequency, specified for LDB, is 595MHz. So, please ask the customer to select the clock source with lower frequency for LDB.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Artur san,

Thank you for your reply.

We will check them.

Best Regards,

Koichi sakagami

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Artur san,

We checked the LDB root clock frequency from PLL5 output.

It was 497.656MHz.

So could you tell us the other way to solve this problem ?

Best Regards,

Koichi Sakagami