- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- How to generate 24.576MHz(CLKO1) from 24MHz(OSC) in SABRE SD board?

How to generate 24.576MHz(CLKO1) from 24MHz(OSC) in SABRE SD board?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Freescale,

I want to generate 24.576Mhz to CLKO1.

I tried the CCM configration with Audio PLL register (CCM_ANALOG_PLL_AUDIO / CCM_ANALOG_PLL_AUDIO_NUM / CCM_ANALOG_PLL_AUDIO_DENOM).

Plase let me konw how to generate 24.576MHz(CLKO1) from 24MHz(OSC) and if possible, provide reference code(clk-imx6q.c).

[Information]

CPU : i.MX6Q

-SW : imx-3.14.28-1.0.0_ga

Thanks,

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jackey

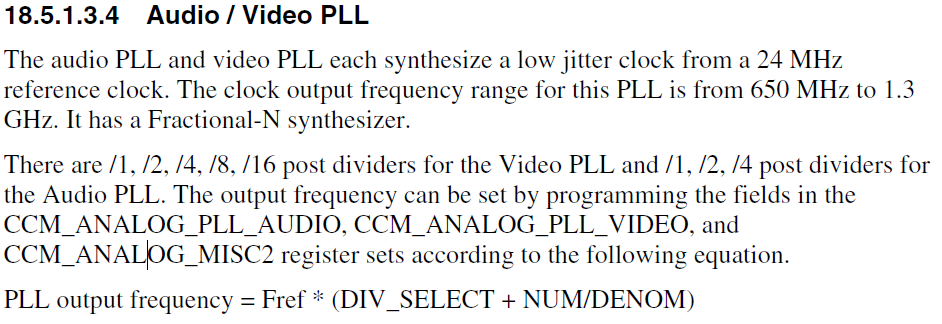

one can try to configure PLL for 737.28MHz (24.576=737.28/30) with

DIV=30, NUM=72, DENOM=100 and dividing with ssi_clk_pred, with ssi_clk_podf,

output ssi_clk_root on CLKO.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

I have succeed to generate 24.576Mhz to CLK1 with your configuration.

Thank you so much.

Jackey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thanks for your message.

I understood your PLL configration(DIV=30, NUM=72, DENOM=100).

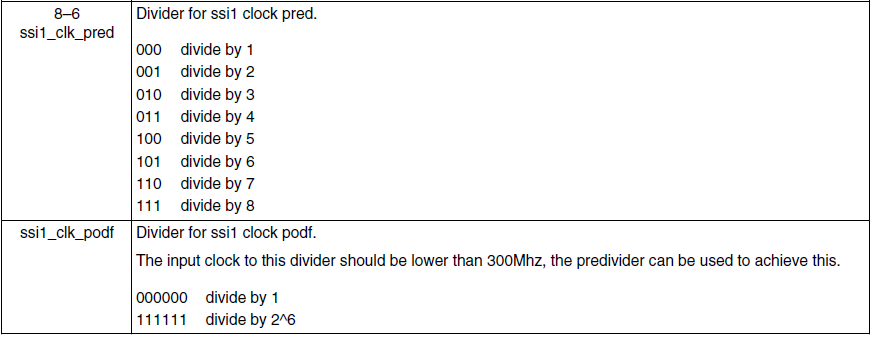

But How to configure 30 devider(24.576=737.28/30) with ssi_clk_pred and ssi_clk_podf?

[ssi1_clk_pred and ssi1_clk_podf register - 20C_4028h]

Please let me konw ssi clk pred and ssi clk podf configration.

Thanks,

Jackey

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jackey

for 30 divider one can select

ssi_clk_pred=100 (divide by 5)

ssi_clk_podf=101 (divide by 6)

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jackey

one can try to configure PLL for 737.28MHz (24.576=737.28/30) with

DIV=30, NUM=72, DENOM=100 and dividing with ssi_clk_pred, with ssi_clk_podf,

output ssi_clk_root on CLKO.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------