- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- K66 CAN INT

K66 CAN INT

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We took over the project from K60 to K66. With the same initialization, the interrrupt no longer works. What is the difference.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I checked the CAN0 and CAN1 interrupt setting code with problem.

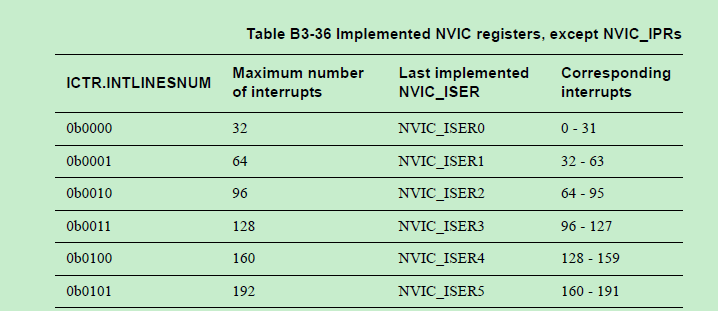

As ARM Cortex M4 core shows the interrupt set-enable registers shows the IRQ number (IRQ) with related register:

For the CAN0 interrupt IRQ value from 75 to 80, which need to use NVIC_ISER2 register to enable CAN0 interrupt.

The CAN1 interrupt IRQ value from 94 to 99, which need to use NVIC_ISER2 and NVIC_ISER3 to enable related CAN1 interrupt.

Please refer below code, which is for K70_120MHz product to enable interrupt function:

/***********************************************************************/

/*

* Initialize the NVIC to enable the specified IRQ.

*

* NOTE: The function only initializes the NVIC to enable a single IRQ.

* Interrupts will also need to be enabled in the ARM core. This can be

* done using the EnableInterrupts macro.

*

* Parameters:

* irq irq number to be enabled (the irq number NOT the vector number)

*/

void enable_irq (int irq)

{

int div;

/* Make sure that the IRQ is an allowable number. Right now up to 105 is

* used.

*/

if (irq > 105)

printf("\nERR! Invalid IRQ value passed to enable irq function!\n");

/* Determine which of the NVICISERs corresponds to the irq */

div = irq/32;

switch (div)

{

case 0x0:

NVICICPR0 |= 1 << (irq%32);

NVICISER0 |= 1 << (irq%32);

break;

case 0x1:

NVICICPR1 |= 1 << (irq%32);

NVICISER1 |= 1 << (irq%32);

break;

case 0x2:

NVICICPR2 |= 1 << (irq%32);

NVICISER2 |= 1 << (irq%32);

break;

case 0x3:

NVICICPR3 |= 1 << (irq%32);

NVICISER3 |= 1 << (irq%32);

break;

}

}

Wish it helps.

Best regards,

Ma Hui

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

If you are using K60_120MHz product and port to K66 product, the interrupt vector assignment has changed:

K60_120MHz product CAN0 interrupt vector from 45 to 50, CAN1 interrupt vector from 53 to 58;

K66 product CAN0 interrupt vector from 91 to 96, CAN1 interrupt vector from 110 to 115;

More detailed info, please check each reference manual chapter3.

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks for the answers.

I set the numbers correctly. But doesn't work. In the Register i can see the data.

Here my init Code:

MK66F18.h

[...]

CAN0_ORed_Message_buffer_IRQn = 75, /**< CAN0 OR'd message buffers interrupt */

CAN0_Bus_Off_IRQn = 76, /**< CAN0 bus off interrupt */

CAN0_Error_IRQn = 77, /**< CAN0 error interrupt */

CAN0_Tx_Warning_IRQn = 78, /**< CAN0 Tx warning interrupt */

CAN0_Rx_Warning_IRQn = 79, /**< CAN0 Rx warning interrupt */

CAN0_Wake_Up_IRQn = 80, /**< CAN0 wake up interrupt */

[..]

CAN1_ORed_Message_buffer_IRQn = 94, /**< CAN1 OR'd message buffers interrupt */

CAN1_Bus_Off_IRQn = 95, /**< CAN1 bus off interrupt */

CAN1_Error_IRQn = 96, /**< CAN1 error interrupt */

CAN1_Tx_Warning_IRQn = 97, /**< CAN1 Tx warning interrupt */

CAN1_Rx_Warning_IRQn = 98, /**< CAN1 Rx warning interrupt */

CAN1_Wake_Up_IRQn = 99 /**< CAN1 wake up interrupt */

[...]

I init the Can 1 and 2:

CANX->CTRL1 &= ~(CAN_CTRL1_CLKSRC_MASK); CTRL1[CLK_SRC] bit. (OSCCLK)

CANX->MCR &= ~(CAN_MCR_MDIS_MASK);

while((CAN_MCR_LPMACK_MASK & CANX->MCR));

while(!(CAN_MCR_FRZACK_MASK & CANX->MCR));

CANX->MCR |= CAN_MCR_IRMQ_MASK;

CANX->MCR |= CAN_MCR_WRNEN_MASK;

CANX->MCR &= ~(CAN_MCR_SRXDIS_MASK);

CANX->MCR |= CAN_MCR_AEN_MASK;

CANX->MCR |= CAN_MCR_LPRIOEN_MASK;

can_init_BAUD( baudrateKHz , X , 12000000 );

I init the CAN 0 Int.:

NVIC->ICPR[ 0 ] = ( NVIC->ICPR[ 0 ] & ~(((uint32_t)0x07)<<29)) | (((uint32_t)0x07)<<29); /* Clear pending interrupt CAN0 */

NVIC->ISER[ 0 ] = ( NVIC->ISER[ 0 ] & ~(((uint32_t)0x07)<<29)) | (((uint32_t)0x07)<<29); /* enable interrupt CAN0 */

NVIC->ICPR[ 1 ] = ( NVIC->ICPR[ 1 ] & ~(((uint32_t)0x1F)<<0)) | ((uint32_t)0x1F); /* Clear pending interrupt CAN0 */

NVIC->ISER[ 1 ] = ( NVIC->ISER[ 1 ] & ~(((uint32_t)0x1F)<<0)) | ((uint32_t)0x1F); /* enable interrupt CAN0 */

I init the CAN 1 Int.:

NVIC->ICPR[ 1 ] = ( NVIC->ICPR[ 1 ] & ~(((uint32_t)0xFF)<<5)) | (((uint32_t)0xFF)<<5); /* Clear pending interrupt CAN1*/

NVIC->ISER[ 1 ] = ( NVIC->ISER[ 1 ] & ~(((uint32_t)0xFF)<<5)) | (((uint32_t)0xFF)<<5); /* enable interrupt CAN1*/

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I checked the CAN0 and CAN1 interrupt setting code with problem.

As ARM Cortex M4 core shows the interrupt set-enable registers shows the IRQ number (IRQ) with related register:

For the CAN0 interrupt IRQ value from 75 to 80, which need to use NVIC_ISER2 register to enable CAN0 interrupt.

The CAN1 interrupt IRQ value from 94 to 99, which need to use NVIC_ISER2 and NVIC_ISER3 to enable related CAN1 interrupt.

Please refer below code, which is for K70_120MHz product to enable interrupt function:

/***********************************************************************/

/*

* Initialize the NVIC to enable the specified IRQ.

*

* NOTE: The function only initializes the NVIC to enable a single IRQ.

* Interrupts will also need to be enabled in the ARM core. This can be

* done using the EnableInterrupts macro.

*

* Parameters:

* irq irq number to be enabled (the irq number NOT the vector number)

*/

void enable_irq (int irq)

{

int div;

/* Make sure that the IRQ is an allowable number. Right now up to 105 is

* used.

*/

if (irq > 105)

printf("\nERR! Invalid IRQ value passed to enable irq function!\n");

/* Determine which of the NVICISERs corresponds to the irq */

div = irq/32;

switch (div)

{

case 0x0:

NVICICPR0 |= 1 << (irq%32);

NVICISER0 |= 1 << (irq%32);

break;

case 0x1:

NVICICPR1 |= 1 << (irq%32);

NVICISER1 |= 1 << (irq%32);

break;

case 0x2:

NVICICPR2 |= 1 << (irq%32);

NVICISER2 |= 1 << (irq%32);

break;

case 0x3:

NVICICPR3 |= 1 << (irq%32);

NVICISER3 |= 1 << (irq%32);

break;

}

}

Wish it helps.

Best regards,

Ma Hui

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear,

it`s working fine.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

Please tell us the whole part number of the two chips.

And please describe detail about your project , and how to porting it 。 You'd better provide the project .

BR

Alice