- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for QorIQ

- :

- CodeWarrior Cache view does not behave as expected (or e5500 issue?)

CodeWarrior Cache view does not behave as expected (or e5500 issue?)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I use CodeWarrior Development Studio 10.4.0 with a T1040RDB board. I am investigating a strange behaviour around L1 caches of the e5500 core (mine is Version: 2.0, 0x80241020) . I wanted to find help with the Cache view in CodeWarrior but that is even more strange...

Are there any errata documents about e5500 caches? I haven't found.

Anyway, here is the initial purpose of my post:

Description

U-Boot locks 3 ways of the L1 data cache. When I stop U-Boot with the CodeWarrior debugger (just after the DRAM initalization) to inspect the cache, I see:

All locked cache lines have a different address and LRU but other properties are the same:

- Dirty: Yes

- Lock: Yes

- Valid: Yes

- Share: No

- Data: zero values

Comments and questions

1. The first strange point is the data content. U-Boot locks some ways to use this space as memory. Is the view known to miss some things (like data display)?

2. In the cache view context menu, I choose "Flush" but the only property that changes is "Valid", that is set to "No". That should not change this property but "Dirty".

If instead of "Flush", I choose "Invalidate", properties "Dirty" and "Valid" are set to "No", as expected.

3. Still from the menu, if I choose "Invalidate Line" or "Flush Line", the result is the same: lines are turned "Dirty: Yes" and "Valid: No". That does not seem to be coherent.

4. Setting a breakpoint in the U-Boot code, I execute flush_dcache(), that has no effect, I still see: "Dirty: Yes", "Lock: Yes", "Valid: Yes"... The lines should be cleaned.

Just after, I call invalidate_dcache(), and I get: "Dirty: No", "Lock: Yes", "Valid: No".

5. After a printf, I see that some lines are shown are "Lock: No"! How is it possible? Is there a problem with the "Cache" view or in an lower-level part?

Thanks,

Mathias

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Mathias Parnaudeau,

I use CodeWarrior 10.5 to connect the T1040RDB board, when the cache able data are accessed, they all could be viewed correctly in the content table. So I think the data display depends on if they've been load into cache line.

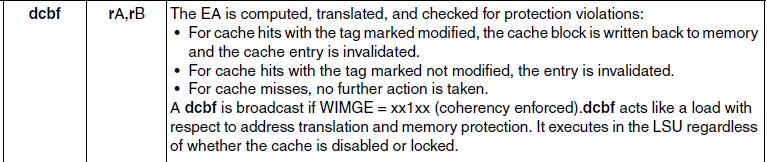

For the "Flush" operation, it's normal the "Valid" changing to "NO", as I understand, flush means data written back from cache to memory and invalidation corresponding cache. See below:

In the same way, "Invalidate" and "Flush" looks similar in the cache, the difference is whether data is written back.

Have a great day,

Lunmin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Mathias Parnaudeau,

I use CodeWarrior 10.5 to connect the T1040RDB board, when the cache able data are accessed, they all could be viewed correctly in the content table. So I think the data display depends on if they've been load into cache line.

For the "Flush" operation, it's normal the "Valid" changing to "NO", as I understand, flush means data written back from cache to memory and invalidation corresponding cache. See below:

In the same way, "Invalidate" and "Flush" looks similar in the cache, the difference is whether data is written back.

Have a great day,

Lunmin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, lunminliang.

I missed that: dcbf flushes and invalidates the data cache block. So that turns off the Valid bit. That answers questions 2 and 3 (even if nothing is said about what theoretically happens to the Dirty bit).

And I also see that "dcbst is implemented identically to dcbf".