- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- LS1021ATWR eTSEC1 not functional

LS1021ATWR eTSEC1 not functional

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Greetings,

I am building SDK v1.8 for the LS1021A TWR board, using GCC 4.8.4. I modified the U-Boot environment to boot via TFTP. eTSEC2 and 3 work, but eTSEC1 cannot communicate. It establishes link at 1Gbps, however I never see Tx packets show up at the switch. eTSEC1 sets up as eth0 in Linux, but does not work there either.

I verified that the HW is using NOR flash 0 RCW and that RCW is SSR_PPN_20. SW2 and SW3 are at defaults.

Is there something I must do in order to get all 3 network interfaces functional? What further information can I provide?

Thank you,

Maury Anderson

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Maury Anderson,

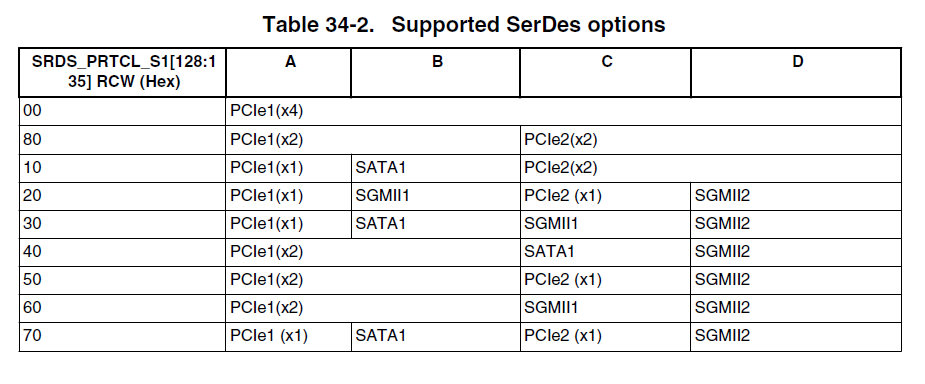

According to your u-boot log, it seems that you use RCW RSR_PPS_70/rcw_1000.bin, the setting of this RCW is 1 SGMII, 1 RGMII, 1SATA, 2PCIE, CAN, SAI, please refer to the the following SerDes options, that's why eTSEC1 cannot work. Please use RCW SSR_PPN_20/rcw_1000.bin in the pre-built image ISO, and please make sure that you flash the RCW on the correct bank.

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Maury Anderson,

Do you use LS1021ATWR CPU Rev1.0 or Rev2.0 board?

Would you please provide u-boot and Linux Kernel boot log?

Please setup eth0 and provide the result of "ethtool eth0".

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Greetings Yiping,

Thank you for your response. Here is my attempt to satisfy the request for information. I have doubts, based on ethtool information, that we are using eTSEC1 in a valid way.

Thanks for your help,

Maury

############################################################

Revision Data

############################################################

Silkscreen on circuit card is: (c) 2014 LS-1021A

There are 3 labels on circuit card containing revision details:

700-28040 REV C

SCH-28040 REV D1

CPLD v2.3 LS1021A SDK v1.3

############################################################

Boot Output

############################################################

U-Boot 2015.01-RCLinux-NewShinyDevKit (Sep 09 2015 - 13:23:58)

CPU: Freescale LayerScape LS1021E, Version: 1.0, (0x87081110)

Clock Configuration:

CPU0(ARMV7):1000 MHz,

Bus:300 MHz, DDR:800 MHz (1600 MT/s data rate),

Reset Configuration Word (RCW):

00000000: 0608000a 00000000 00000000 00000000

00000010: 70000000 00407900 e0025a00 21046000

00000020: 00000000 00000000 00000000 00038000

00000030: 00080000 48007340 00000000 00000000

Board: LS1021ATWR

CPLD: V2.3

PCBA: V4.0

VBank: 0

I2C: ready

DRAM: 1 GiB

Using SERDES1 Protocol: 112 (0x70)

Firmware 'Microcode version 0.0.0 for T1040 r1.0' for 1040 V1.0

QE: uploading microcode 'Microcode for T1040 r1.0'

Flash: 128 MiB

MMC: FSL_SDHC: 0

EEPROM: CRC mismatch (3b162798 != ffffffff)

PCIe1: Root Complex no link, regs @ 0x3400000

PCIe2: Root Complex no link, regs @ 0x3500000

In: serial

Out: serial

Err: serial

SEC0: RNG instantiated

SATA link 0 timeout.

AHCI 0001.0300 1 slots 1 ports ? Gbps 0x1 impl SATA mode

flags: 64bit ncq pm clo only pmp fbss pio slum part ccc

scanning bus for devices...

Found 0 device(s).

SCSI: Net: eTSEC2 is in sgmii mode.

eTSEC1 [PRIME], eTSEC2, eTSEC3

Hit any key to stop autoboot: 0

eTSEC1 Waiting for PHY auto negotiation to complete. done

Speed: 1000, full duplex

Using eTSEC1 device

TFTP from server 10.10.0.1; our IP address is 10.10.0.100

Filename 'ls1021twr0/uImage'.

Load address: 0x80020000

Loading: T T T T T T T T T T

Retry count exceeded; starting again

Speed: 1000, full duplex

Using eTSEC2 device

TFTP from server 10.10.0.1; our IP address is 10.10.0.100

Filename 'ls1021twr0/ls1021a-twr.dtb'.

Load address: 0x80000000

Loading: ##

1.5 MiB/s

done

Bytes transferred = 21046 (5236 hex)

Speed: 1000, full duplex

Using eTSEC2 device

TFTP from server 10.10.0.1; our IP address is 10.10.0.100

Filename 'ls1021twr0/rootfs.cpio.uboot'.

Load address: 0x81000000

Loading: #################################################################

#################################################################

#################################################################

#################################################################

################################

1.7 MiB/s

done

Bytes transferred = 4279911 (414e67 hex)

## Booting kernel from Legacy Image at 80020000 ...

Image Name: Linux-3.12.37-rt51-RCLinux-Maury

Image Type: ARM Linux Kernel Image (uncompressed)

Data Size: 3105160 Bytes = 3 MiB

Load Address: 80008000

Entry Point: 80008000

Verifying Checksum ... OK

## Loading init Ramdisk from Legacy Image at 81000000 ...

Image Name:

Image Type: ARM Linux RAMDisk Image (uncompressed)

Data Size: 4279847 Bytes = 4.1 MiB

Load Address: 00000000

Entry Point: 00000000

Verifying Checksum ... OK

## Flattened Device Tree blob at 80000000

Booting using the fdt blob at 0x80000000

Loading Kernel Image ... OK

Loading Ramdisk to beb0f000, end bef23e27 ... OK

Loading Device Tree to beb06000, end beb0e235 ... OK

Starting kernel ...

i2c i2c-2: of_i2c: modalias failure on /soc/i2c@21a0000/ltc2945@67

layerscape-pcie 3400000.pcie: phy link never came up

layerscape-pcie 3500000.pcie: phy link never came up

sgtl5000 1-000a: Failed to get supply 'VDDD': -19

drivers/rtc/hctosys.c: unable to open rtc device (rtc0)

Starting logging: OK

Initializing random number generator... done.

Starting network...

udhcpc (v1.23.1) started

Sending discover...

Sending discover...

Sending discover...

Sending select for 10.10.1.74...

Lease of 10.10.1.74 obtained, lease time 86400

adding dns 10.10.0.1

Welcome to Linux

devkit login:

############################################################

Ethtool Output

############################################################

# ethtool eth0

Settings for eth0:

Supported ports: [ MII ]

Supported link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

1000baseT/Full

Supported pause frame use: Symmetric Receive-only

Supports auto-negotiation: Yes

Advertised link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

1000baseT/Full

Advertised pause frame use: No

Advertised auto-negotiation: Yes

Speed: 1000Mb/s

Duplex: Full

Port: MII

PHYAD: 2

Transceiver: external

Auto-negotiation: on

Supports Wake-on: uag

Wake-on: d

Current message level: 0x0000003f (63)

drv probe link timer ifdown ifup

Link detected: yes

#

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Maury Anderson,

According to your u-boot log, it seems that you use RCW RSR_PPS_70/rcw_1000.bin, the setting of this RCW is 1 SGMII, 1 RGMII, 1SATA, 2PCIE, CAN, SAI, please refer to the the following SerDes options, that's why eTSEC1 cannot work. Please use RCW SSR_PPN_20/rcw_1000.bin in the pre-built image ISO, and please make sure that you flash the RCW on the correct bank.

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Based on this tab, I wonder how can I use eTSEC0 as SGMII , eTSEC1 and eTSEC2 as RGMII, it seems like SGMII1 and SGMII2 must be configured at the same time

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am facing same issue i.e eTSEC1 is not working while eTSEC2 and eTSEC3 are working. I have posted this in below thread.

https://community.nxp.com/thread/439364

Any help is highly appreciated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Romit, I posted comment here, where I described that I think the MUX is improperly switched. Noone said I am wrong, noone posted a CPLD source matching the label on our Tower board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dusan,

Thanks for your reply. I think MUX is properly switched and also according to board specification (TWR-LS1021ARM), eTSEC ports do not depend on any switch setting.

Are you still facing this issue of eTSEC1 not working while eTSEC2 and eTSEC3 are working? Have you found any solution?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I see this is relevant thread to post my rcw_1000.rcw recompilation issue.

My custom board is bit different than the reference board LS1021TWR, so i have modified the RCW bits according to my board using CW dev studio+QCVS tool and using it.

I want to include this as part of Yocto tree and build it along with other images(linux kernel,u-boot,RFS etc).

So i had generated pbl.pbl file from CW dev studio and modified rcw_1000.rcw file under /rcw/git-r0/git/nextflash/SSR_PNS_30/ path,but the issue is only when i do the cleanstate build using bitbake it builds this file else it will not recompile this file.

If someone is aware of how to recompile without doing cleanstate with bitbake(as it takes nearly 1 hour to recompile the tree),kindly help me out.

Best Regards,

Nagi