- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- K64F MCU on custom board not replying with genuine Segger J-Link using SWD.

K64F MCU on custom board not replying with genuine Segger J-Link using SWD.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

K64F MCU on custom board not replying with genuine Segger J-Link using SWD.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I made my own custom board using the MK64FN1M0VLL (same as on the Freedom K64F Mbed board) but I am having issues with flashing it (K64F not seeming to reply to any SWD commands). I have a feeling this is happening because the micro controller is not being correctly put and kept in a reset state when it should during SWD communications. To be clear, this is an un-programmed K64F fresh from the factory.

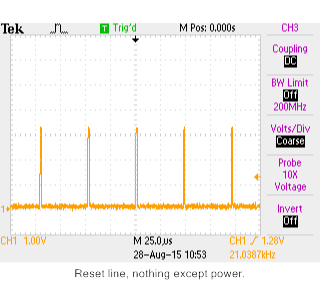

Below is the reset line when power is applied to the K64F. The line going high seems to make sense based on the MCU resetting itself due to as I understand this post here.

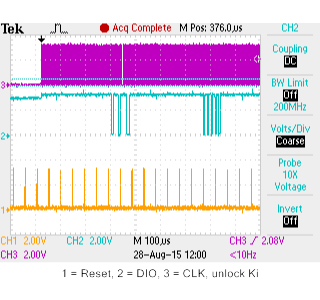

And here is me running an "unlock Kinetis" command in J-Link commander. Shouldn't reset be held low during this time?

There is a 50 uS gap between every 1.5 uS long spike at 3.3v.

Power is from USB 5V -> ferrite bead -> 10 uF capacitor -> 0.1 uF decoupling capacitor -> K64F 5v to 3.3v regulator -> 2.2 uF 3.3v output -> all VCC pins with their own 0.1 uF decoupling caps

I am using the internal regulator on the K64F to convert the USB 5 volts to 3.3 volts which is being used to power the K64F.

- USB 5 volts has 10 uF decoupling cap after ferrite bead.

- VREGIN connected to USB 5 volts and has 0.1 uF decoupling cap.

- VOUT33 (Pin 12) has 2.2 uF decoupling cap.

- EZP_CS/NMI (PTA_4, Pin 38) pulled up with a 4.7k resistor.

- SWD_CLK (PTA0, Pin 34) pulled up with a 100k resistor (as per ARM recommendations).

- SWD_DIO (PTA3, Pin 37) pulled up with a 100 k resistor (as per ARM recommendations).

- Reset (Pin 52) pulled up with a 4.7k resistor (no 0.1 uF cap).

- All VDD/VSS pairs have 0.1 uF decoupling caps.

- VDDA + VREFH connected to 3.3v and VSSA + VREFL connected to ground, share a single 0.1uF decoupling cap.

I connected Reset, SWD_DIO, SWD_CLK, Ground, and 3.3v (VTref, J-link uses this to sense the target voltage) to the Segger J-Link adapter.

Any suggestions on what the reset line should be doing during SWD communication? If I pull it low myself by removing the 4.7k pullup and adding a 4.7k pulldown, should the programming process still work? Are the Kinetis devices locked when fresh out of the factory?

Or, even better, does Freescale have bare minimum example for a K64F MCU to be able to be programmed fresh out of a factory using SWD?

Thank you for any potential help,

Marcin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Oh yeah, and here is the communication for the Segger J-Link adapter, which has been updated to the newest version:

VTarget = 3.217V

Info: TotalIRLen = ?, IRPrint = 0x..000000000000000000000000

Info: TotalIRLen = ?, IRPrint = 0x..000000000000000000000000

No devices found on JTAG chain. Trying to find device on SWD.

No device found on SWD.

Trying to find device on FINE interface.

No device found on FINE interface.

Did not find any core.

Failed to identify target. Trying again with slow (4 kHz) speed.

No devices found on JTAG chain. Trying to find device on SWD.

No device found on SWD.

Trying to find device on FINE interface.

No device found on FINE interface.

Did not find any core.

No device found at all. Selecting JTAG as default target interface.

J-Link>exec device = MK64FN1M0xxx12

Info: Device "MK64FN1M0XXX12" selected.

J-Link>si 1

Selecting SWD as current target interface.

Setting target interface speed to 1MHz. Use "Speed" to change.

J-Link>speed 100

Target interface speed: 100 kHz

J-Link>unlock Kinetis

ERROR: Could not reset error in Ctrl/Stat register.Unlocking device...ERROR: Rea

d from DP/AP register failed!

J-Link>erase

Erasing device (MK64FN1M0xxx12)...

ERROR: Erase returned with error code -1.

J-Link>

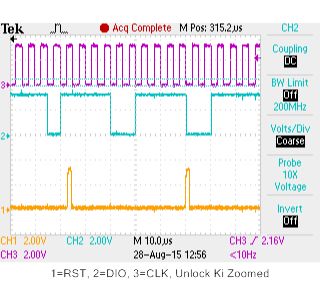

And the zoomed in initial 3 dips on the SWD_DIO line:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

SWD_CLK should be pull-down not pull-up. Please modify it and have a try again.

Best Regards

Paul

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After a few days of debugging, I found out what my issue was. I reversed the silkscreen for SWD_Trace and SWD_CLK on my PCB, causing me to always plug in SWD_CLK into SWD_Trace, hence the chip never seeming to reply. Whoops!

Turns out that SWD_CLK being pulled up via a 100k resistor makes it still work though, but for the next revision I will pull them down using a 100k resistor. Thanks for your help!