- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- About eMMC boot failure in i.MX6DL.

About eMMC boot failure in i.MX6DL.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

About eMMC boot failure in i.MX6DL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear All,

[Overview]

Device : i.MX6DL + PF0100A

OS/Version : Linux L3.0.35_4.1.0

Issue : Repeart the Re-boot

Failure rate : 10 per 22,000units (Very rare units)

Target Board : Custom board

Detail :

The custom board boot-up from eMMC.

But, the failure board repeat the re-boot because of changing the status bit on eMMC (DEVICE is locked).

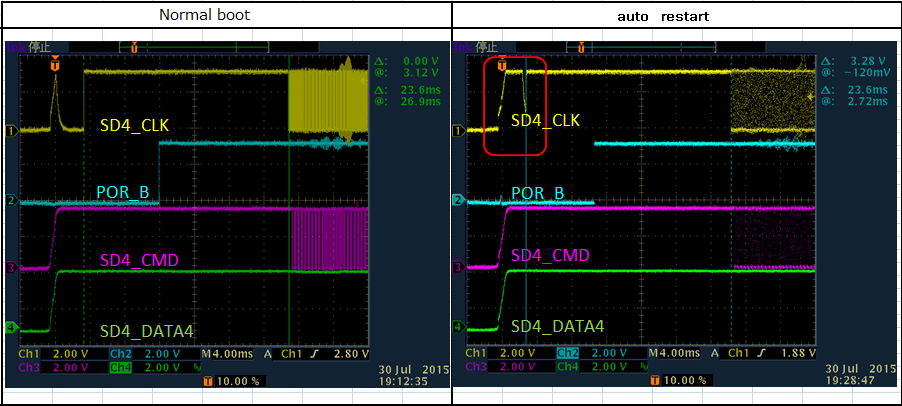

My customer measured the waveform between i.MX and eMMC at boot-up.

The waveform found the different about behavior of SD4_CLK.

*Refer to below waveform.

We want to confirm the whether or not right operation.

[Question]

Could you give me an advice about the possible causes?

(Does On-chip boot ROM in i.MX6 have an influence?)

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please take a look at the "auto restart" screenshot, the POR_B (blue) trace under the red rectangle, highlighting the abnormal glitch on the SD4_CLK signal. You can see a short glitch on the POR_B signal, that can affect the normal boot sequence. The presence of the glitch points to the fact that either the power-up sequence is violated or the initial ramp-up of a main power is unstable. Please double-check that points.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

Thank you for your reply.

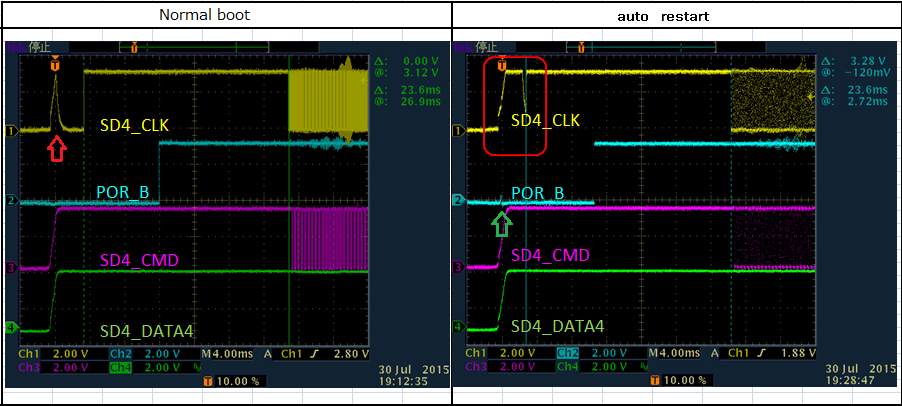

Refer to below waveform again.

[Q1]

Refer to red arrow in the "Normal boot".

- Why does glitch on the SD4_CLK occur? (We want to know the mechanism.)

The red arrow looks not glitch. I think that Internal 100kOhm Pull-up effect at the red arrow point.

After that, i.MX6 forces to Low on the SD4_CLK line, isn't it?

- Is this glitch right operation?

- And, Is there possibility that the glitch has an influence on boot?

- Is the factor of glitch i.MX6? (or external eMMC)?

[Q2]

>You can see a short glitch on the POR_B signal, that can affect the normal boot sequence.

Refer to green arrow in the "auto restart".

Is this your mentioned point?

The glitch is very small. So I consider that the glitch cannot affect the boot sequence.

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

A1. The glitch you've pointed by the red arrow just follows the initial power

ramp-up until the internal reset occurs and the SD4_CLK pin switches to its SDHC

function. It is produced by i.MX6, it is normal and does not affect the boot

procedure.

A2. Yes, I mean the glitch you've pointed by the green arrow on the "auto

restart" screenshot. It _can_ affect the boot sequence, although you may not see

it clearly on the oscilloscope. Especially, if it is caused by a main power

instability during initial power-up. So, double-check what's wrong with the main

power on malfunctioning boards.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

Hello. I update the below thing.

> A2. Yes, I mean the glitch you've pointed by the green arrow on the "auto

> restart" screenshot. It _can_ affect the boot sequence, although you may not see

> it clearly on the oscilloscope.

My customer measured the detail waveform about POR_B glitch with hot & cold temperature.

Refer to attached file.

We didn't find the critical glitch.

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

just some stupid considerations:

- Is the power supply (external from the board) able to keep boot/working current as mA, and a bit over dimensioned ?

- can you detail a bit the power stage of the schematic, to understand the voltage dropouts ? Are you using a PMIC or a less complex PS stage as for example in sabrelite ?

- Is it possible the power switch produce some glitches ?

- do you have any ripple on the power lines in the faulty boards ?

Regards,

angelo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Angelo,

This phenomenon found on custom board.

Maybe, it will appear on SABRE-SDP, too.

My customer is researching, and the other problem was not found.

(Main power stable, sequence are OK. Other glitch was not found.)

We want to clear the behavior of SD4_CLK mechanism by changing temperature.

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It makes sense to check the board regarding the recent Design checklist,

in particular : number, nomenclature and location of (bulk) capacitors.

Regards

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Yuri,

Hello. Thank you for your reply.

We want to understand about SD4_CLK behavior.

Refer to the "SD4_CLK_Operation(150828).xlsx" file again.

[Q1]

We think that the SD4_CLK behavior caused by i.MX6 output.

How do you think?

[Q2]

> in particular : number, nomenclature and location of (bulk) capacitors.

Where capacitor did you point out?

[Q3]

I referred the check list and found the only below item.

Could you check it?

[From HW Design Checking List for i.MX6DQSDL (Rev.2.8)]

NAND_RE and SDx_CLK are loop back as internal reference clock at internal pad, recommend adding a series 0hom resister on these two signals and place near i.Mx6 pin side to reduce the potential reflect SI issue.”

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Arthur mentioned about signal's glitches - this may be caused by noisy environment,

assuming under proper conditions i.MX6 is working fine. So, please check Table 2-6 (Power

and decouple recommendations) of http://cache.freescale.com/files/32bit/doc/user_guide/IMX6DQ6SDLHDG.pdf

Also, PCB layout inaccuracy may influence on signals. Please check Chapter 3 (i.MX 6 Series Layout

Recommendations). Note - it makes sense to verify all conditions and signals, mentioned in Layout

recommendations and Design checklist - because of possible cross influence.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please pay attention, the issue takes place during power up, when POR

is still asserted. Note, during power up sequence and short period of stabilization,

pin states are not defined and may demonstrate unusual behavior.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Yuri,

Hello. Thank you for your reply.

I'd like to isolate this problem, which caused by i.MX6 or custom layout.

So, please measure the SD4_CLK on freescale's board to close this question.

1. Is the same phenomenon seen on freescale's board?

If you can see the same phenomenon, does this phenomenon have an influence on the operation of eMMC?

2. If you can not see the same phenomenon, I think that it is customer's specific problem.

Best Regards,

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I see, on the SDB board the SD4_CLK is not accessible :-(

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Yuri,

Hello. Can you measured it on validation board?

Keita

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I do not have it.

~Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

Thank you for your reply.

> A1. The glitch you've pointed by the red arrow just follows the initial power

> ramp-up until the internal reset occurs and the SD4_CLK pin switches to its SDHC

> function.

Refer to attached file [SD4_CLK_Operation(150828).xlsx].

The SD4_CLK waveform changed dependent on the temperature of i.MX6DL.

[Q1]

Is SD4_CLK was right operation as i.MX6DL(SDHC)?

[Q2]

Why does it become such operation dependent on the temperature?

Best regards,

Keita