- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Question about HW_PINCTRL_EMI_DS_CTRL of i.MX28 (RM 9.4.84)

Question about HW_PINCTRL_EMI_DS_CTRL of i.MX28 (RM 9.4.84)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Community,

I have questions about HW_PINCTRL_EMI_DS_CTRL of i.MX28.

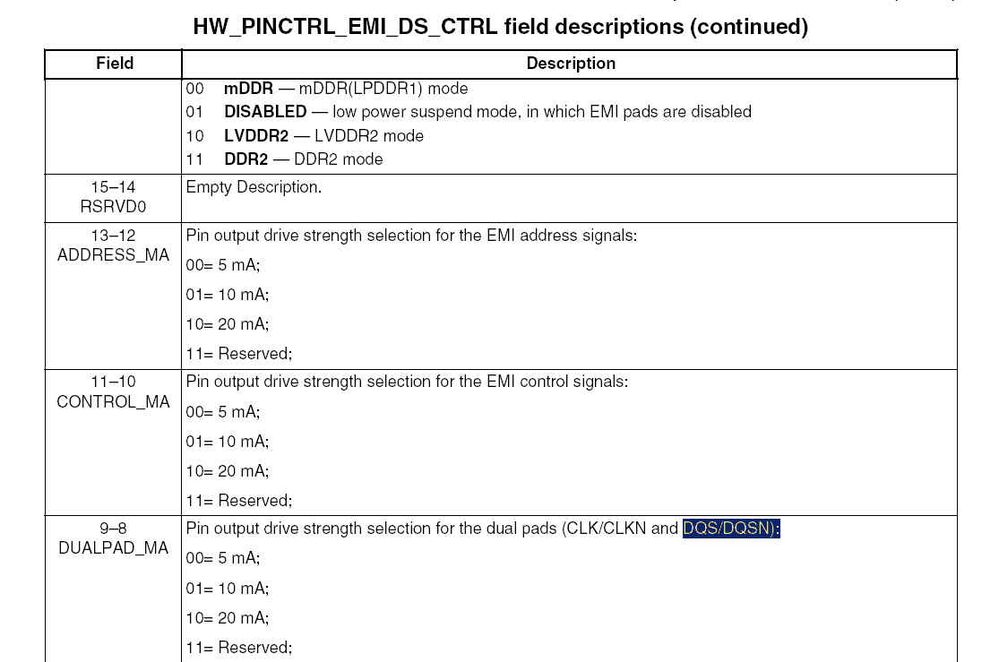

1. Do SLICE0_MA (bit1-0) and SLICE1_MA (bit3-2) set the drive strength of DQM0 and DQM1, too, as well as DQ[00:15],

or the drive strength of DQM is defined by CONTROL_MA (bit11-10)?

2. Which defines the drive strength of DQS/DQSN, DUALPAD_MA or SLICE1/0_MA?

I searched the log of the Community and found a post which mentions that SLICE is related to data, mask, strobe.

https://community.freescale.com/message/479777#479777

But since the description in 9.4.84 of RM shows that the drive strength of DQS/DQSN is set by DUALPAD_MA, I am not sure what SLICE is.

Could anyone please give me the answer to the questions above?

Thank you,

Hikaru Uruno

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hikaru

1. yes DQM0 and DQM1 is set by SLICE0_MA

2. DQS/DQSN is set by DUALPAD_MA

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hikaru

1. yes DQM0 and DQM1 is set by SLICE0_MA

2. DQS/DQSN is set by DUALPAD_MA

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thank you for the answers!

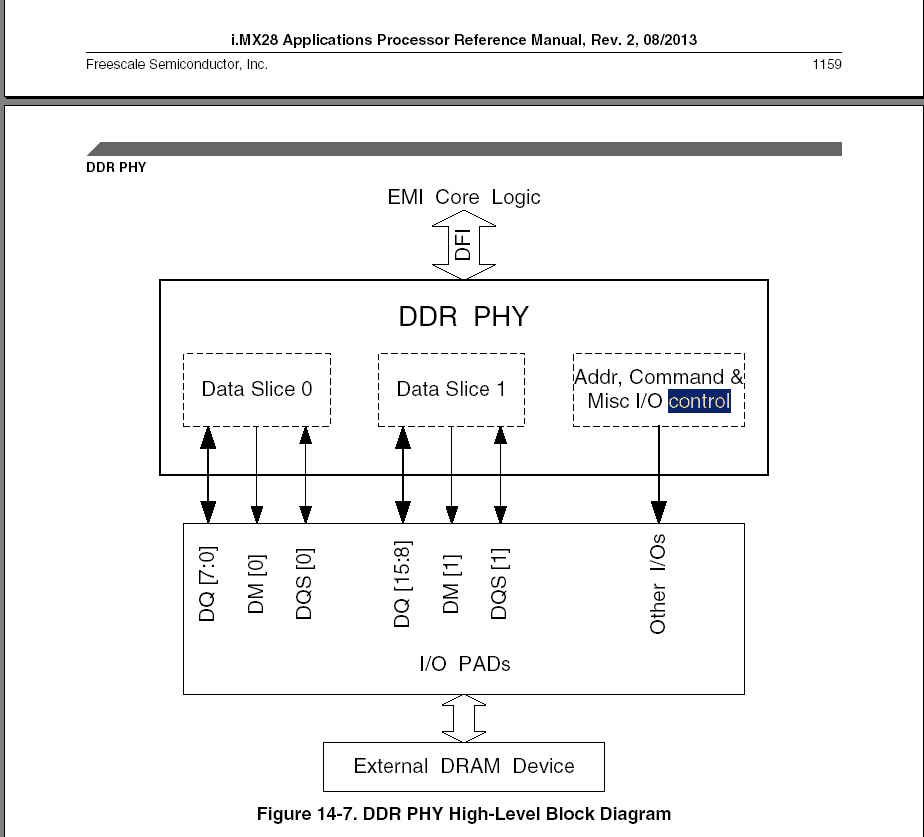

It looks strange that even though Figure 14-7 shows that DQSs are a part of the slices, the drive strength of DQSs is not defined by SLICEx_MA but by DUALPAD_MA...

Best regards,

Hikaru

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hikaru

these are exceptions which are specially mentioned in

DUALPAD_MA description.

Best regards

~igor