- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- T-Series

- :

- whether roll-over time need to consider in the Global timer base count value?

whether roll-over time need to consider in the Global timer base count value?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are using T2080 based processor board. processor are operating by the below mention frequency.

System Clock is 100Mhz

Platform Clock is 500Mhz

MPIC Clock is 250Mhz

Global Timer is 31.25Mhz (MPIC is the clock source for timer, Prescaler is 1/8).

Time Count for 1sec = 31250000 (decimal)

Time Count for 1msec = 31250 (decimal)

I am setting the 31250 (decimal) value in Global timer base count register (MPIC_GTBCRAn) to configure 1 mili sec timeout and roll-over condition is configured as "GTCCRxn is reloaded with the GTBCRxn value" in the MPIC_TCRn.

Global Timer is running for 3min by the external timer and check the interrupt count. the expected counts is 180000 tolerance may be +/- 1. but only 179994 interrupt counts occurred. Six interrupt counts is missing i.e 6 msec drift is there with that 1msec count value running fro 3 min.

After i changed the base count value from 31250 to 31249 (consider the roll-over time), with this one count less we got the expected 180000 interrupt counts.

(Note: external timer already verified with scope.)

whether roll-over time need to consider in the Global timer base count value?

or

How to manage the clock drift?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The counter states for one clock cycle (t_clk) for each count value. The start count value is the base count value (N). The last count value is 0. After the last state count is repeated in the same way from N to 0. So for each timer period (T_tmr) counter goes through N, N-1, … 1, 0 states and that takes (N+1) clock cycles. Correspondingly

T_tmr = (N+1) * t_clk

It is the same as length of zero-based indexed array. Total number of the array elements is max_index +1. Because there is array element with index 0 in additional to 1, 2 ... max_index elements.

Unfortunately I could not find any app. note for the MPIC global timer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have a great day,

Global Timer toggle interval is equal to (base_count_register_value + 1)*clock_period.

Hence for 3 min we shoud get 179994 interrupt counts because of 31250000*(3*60)/(31250+1)= 179994,2402

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Serguei Podiatchev,

Thanks for your reply.

If i calculated base count for timeout period in msec.

base count = (freq in Hz / 1000) * (timeout period in msec)

e.g: For calculate base count for 10 msec timer timeout value is [((31250000 / 1000 ) * 10) = 312500]

As per your statement, I assumed the base count register value is entered as 312500 for 10msec.

Global Timer timeout interval = (312500 + 1) * 32 nano sec = 10000032 nano sec

i.e) 32nano sec drift will added in every timeout interval.

Why to add plus one with base count register value to calculate Global Timer toggle interval?

I referred other global timer in reference manuals like MPC107, MPC8641D and P1022 processor which is identical to T2080 global timer, no where i found this formula.

This formula is applicable only for T2080 processor other processor or memory controller also which i mention above freescale product.

Is there any application notes is available for calculate the base count value ?

Regards

Karunakaran R

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The counter states for one clock cycle (t_clk) for each count value. The start count value is the base count value (N). The last count value is 0. After the last state count is repeated in the same way from N to 0. So for each timer period (T_tmr) counter goes through N, N-1, … 1, 0 states and that takes (N+1) clock cycles. Correspondingly

T_tmr = (N+1) * t_clk

It is the same as length of zero-based indexed array. Total number of the array elements is max_index +1. Because there is array element with index 0 in additional to 1, 2 ... max_index elements.

Unfortunately I could not find any app. note for the MPIC global timer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Serguei Podiatchev,

Thanks for your information.

Based on your information,I understand Base count register(MPIC_GTBCRAn) value is set it to 0 for generate interrupt in every clock cycle (i.e 32nano sec).

MPIC_GTBCRAn Timeout Time(nano sec)

0 32

1 64

10 352

31250 1000032

31250000 1000000032

As per the formula (T_tmr = (N+1) * t_clk), I have to set the base count register with one count less to get the accurate timer out value of the timer.

But I still have doubts, I referred another (P1022) QorIQ processor reference manual since t2080 processor reference manual does not have example base count value for global timer.

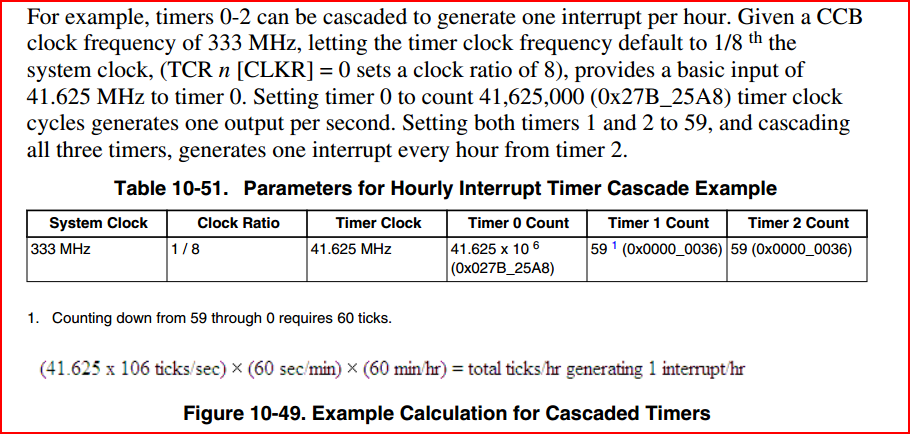

The below example snap shot is taken from the Document Number: P1022RM Rev. 2, 04/2013, section : 10.3.19 Timer control register group n (PIC_TCRn)

The above example is configured for 1hr in cascaded mode. In that Timer0 count value is calculated as 1 sec based on that 41.625Mhz frequency(i.e 0x27B_25A8 value is calculated for 1sec).

Is the P1022 processor global timer also applicable for the same formula to calculate the base count register?, If it is applicable, the timer 0 is configured for 1sec + 24 nano second. this lead to 86 micro second time drift per hour.