- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Design Studio

- :

- Kinetis K22FN512VLH12 - Only using half of the SRAM?

Kinetis K22FN512VLH12 - Only using half of the SRAM?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using KDS 3.0, KSDK 1.2, and a Freedom K22F board.

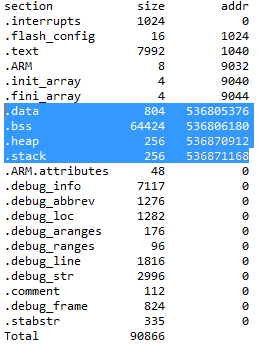

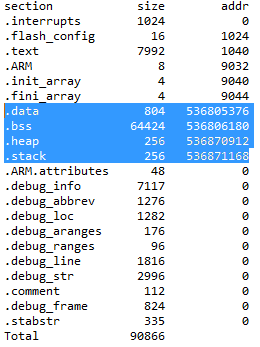

This may be a KDS question, but I'm seeing that .bss is only allowing the use of up to 64k of my SRAM on compile, when I know there are 128k of RAM?

Per the Family Manual :

3.5.3.1 SRAM sizes This device contains SRAM accessed by bus masters through the cross-bar switch. The on-chip SRAM is split into SRAM_L and SRAM_U regions where the SRAM_L and SRAM_U ranges form a contiguous block in the memory map anchored at address 0x2000_0000. As such: • SRAM_L is anchored to 0x1FFF_FFFF and occupies the space before this ending address. • SRAM_U is anchored to 0x2000_0000 and occupies the space after this beginning address.

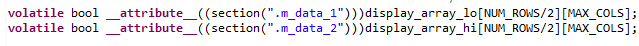

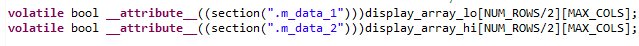

Given that "NOTE Misaligned accesses across the 0x2000_0000 boundary are not supported in the ARM Cortex-M4 architecture", I have broken my large multi-dimensional array in two so that I can place on half in SRAM_L, and the other half in SRAM_U, even if I leave a hole of wasted memory at the boundary. Using the methods from Erich Styger's tutorial : Defining Variables at Absolute Addresses with gcc | MCU on Eclipse , I break my large array into 2, and place them in sections of the memory :

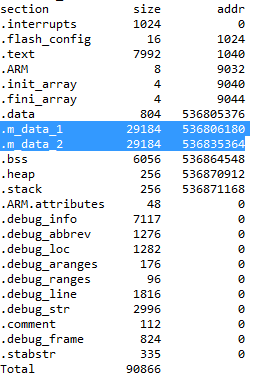

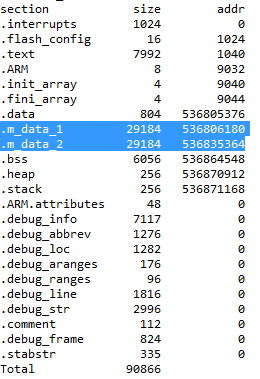

Now it's leveraging the available space of SRAM_U to place the stack and heap, however, it's still limited to 64k total for everything else, and looking at the address values vs the linked file, doesn't appear to be actually putting .m_data_2 at 1FFF7524 instead of the starting address of m_data_2 which is 0x2000_0000?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Donald,

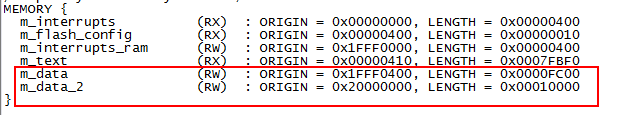

(1) Please check the linker file ("*.ld" file ) , the SRAM :

(2) Please show your linker file , do you want relocate the two array to m_data_1 and m_data_2 ?

If yes, in the SECTIONS part of linker file , you need configure like this :

.mySection1 :

{

*(.m_data_1)

} > m_data_1

.mySection2 :

{

*(.m_data_2)

} > m_data_2

If i misunderstand your question , please tell me .

Have a great day,

Alice

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I was having the same problem and thankfully stumbled on this post. Why would only half the ram be enabled by default?

Thanks for posting!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

the reason is that the Kinetis M4 devices have two memory controllers, one for each area. It is splitted up in the linker file as a burst access over that boundary would generate a hard fault. If this is not a problem for you, you can use it as one memory block.

There has been a discussion on that topic here: FreeRTOS Heap with Segmented Kinetis K SRAM | MCU on Eclipse

I hope this helps,

Erich

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Donald,

(1) Please check the linker file ("*.ld" file ) , the SRAM :

(2) Please show your linker file , do you want relocate the two array to m_data_1 and m_data_2 ?

If yes, in the SECTIONS part of linker file , you need configure like this :

.mySection1 :

{

*(.m_data_1)

} > m_data_1

.mySection2 :

{

*(.m_data_2)

} > m_data_2

If i misunderstand your question , please tell me .

Have a great day,

Alice

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I assumed I could just use the attribute without adding the section, which was incorrect. I have added the section as the tutorial, and you now show, and it's working fine. Thank you!