- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Query on CSI Lanes in i.MX6Q

Query on CSI Lanes in i.MX6Q

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

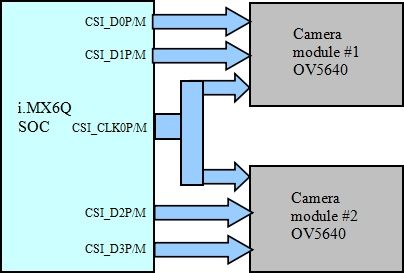

We are planning to interface 2 CSI camera modules each with 2 data lanes to i.MX6Q processor (Camera#1:Dat0 and Dat1, Camera#2 :Dat2 and Dat3) and share the CSI lane Clock for both.

We will not use both the Camera's simultaneously.

Can we configure CSI data lanes Dat2 and Dat3 as lanes Dat0 and Dat1 respectively for the Camera#2? We plan to reuse the same Camera module as Camera#1 for Camera#2.

Is there any way we can inform the processor about this lane allocation?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After some analysing I conclude, that this is impossible to use two MIPI cameras

connected to the MIPI CSI-2 interface of the i.MX6. Because all data lines are used

in complicated MIPI protocol, we cannot split it between two cameras.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

May I ask a question? I'd like to use 2 1080p MIPI cameras to i.MX6Q, is it possible to use it as follow:

- two cameras use the same CLK LANE;

- two cameras work at the same time;

- camera No.1 use the data lane 0~1, Camera No.2 use the data lane 2~3.

If it is feasiable, how to use the the same CLK LANE? is there a special chip to seperate one clk lane to two?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I expect the MIPI CSI-2 interface of the i.MX6 is considered in the thread.

Strictly speaking the mentioned configuration (common clock, two pairs of

data lines from one camera and other two pairs – from the second) is not supported

by the i.MX6 CSI-2 Host Controller, since all the data lines relates to single

camera. Nevertheless Your connection scheme may be implemented, assuming

that only one camera is enabled at time, and the first camera is configured for

two-bits data bus, and the second - for the 4-bits. For the second camera, the

low two bits should be rejected later in software. It may provide some performance

degradation.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Yuri ,

To make things more clear, I have attached the below image. Following is my understanding from your statement.

- We can connect a 2 lane camera to CSI_D2P/M and CSI_D3P/M provided no camera is connected on CSI_D0P/M and CSI_D1P/M.

- We have to enable all the four lanes by setting N_LANES as 11 in MIPI_CSI_N_LANES register of i.MX6Q.

- Reject the lower two lanes of data in software.

Is my above interpretation of your statement correct? Kindly correct me if I am wrong.

Thanks

Vijai

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After some analysing I conclude, that this is impossible to use two MIPI cameras

connected to the MIPI CSI-2 interface of the i.MX6. Because all data lines are used

in complicated MIPI protocol, we cannot split it between two cameras.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Yuri . Thank you for your support :smileyhappy: