- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Kinetis KL02 - using MCGIRCLK in VLPS mode

Kinetis KL02 - using MCGIRCLK in VLPS mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm using a Kinetis KL02 and try to use MCGIRCLK (slow clock) as the TPM Clock Source.

After entering VLPS mode it seams that MCGIRCLK is stopped even though I set IREFSTEN to 1.

Can anybody how to configure the KL02 to use TPM with the internal 32 kHz clock source during VLPS mode?

Thank you

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin Hierold,

You can't use internal 32 kHz clock source during VLPS mode, you just can use 4Mhz IRC clock as the TPM clock source during VLPS mode.

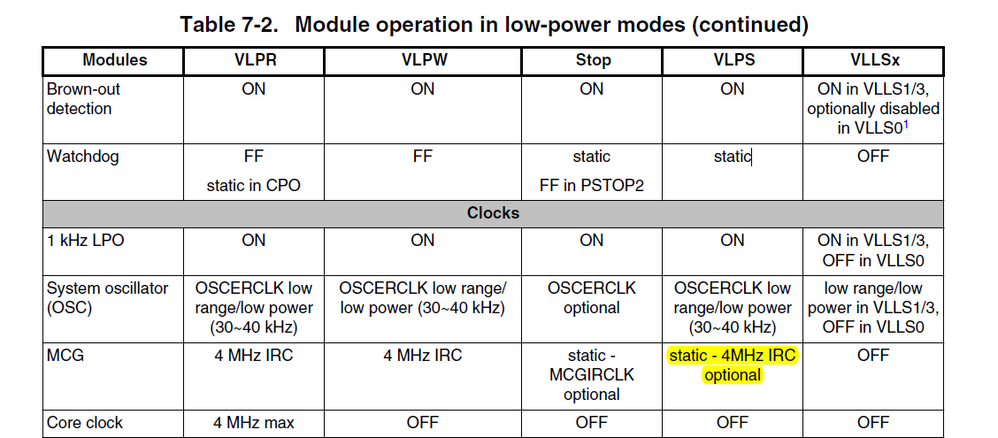

Because in VLPS mode, MCG state is static or 4MHZ IRC, you can find this in the reference manual.

Besides, if you want to use the internal clock 4Mhz as the TPM clock source

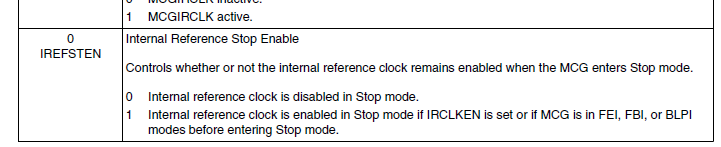

Just set IREFSTEN is not enough, you also need set IRCLKEN

you are not only need to set MCG_C1[IREFSTEN], but also MCG_C1[IRCLKEN ] and MCG_C2[IRCS].

Wish it helps you!

If you still have question, please let me know!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you.

Now it works with the 4MHz IRC.

I didn't read table 7-2 before.

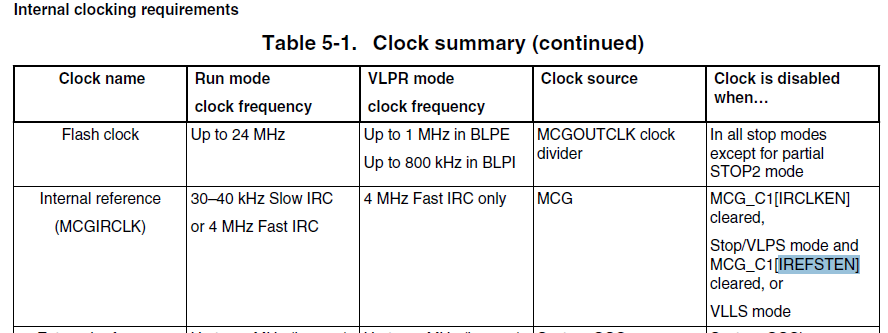

As Mark mentioned I assumed from reading table 5-1 that MCGIRCLK is active in VLPS when IREFSTEN is set no matter if it's the fast or slow IRC.

The register description "21.3.1 MCG Control 1 Register (MCG_C1)" also doesn't state that IREFSTEN only applies for the fast IRC.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Martin Hierold,

You can't use internal 32 kHz clock source during VLPS mode, you just can use 4Mhz IRC clock as the TPM clock source during VLPS mode.

Because in VLPS mode, MCG state is static or 4MHZ IRC, you can find this in the reference manual.

Besides, if you want to use the internal clock 4Mhz as the TPM clock source

Just set IREFSTEN is not enough, you also need set IRCLKEN

you are not only need to set MCG_C1[IREFSTEN], but also MCG_C1[IRCLKEN ] and MCG_C2[IRCS].

Wish it helps you!

If you still have question, please let me know!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I can confirm the behaviour, which makes sense based on details in table 7-2.

However table 5-1 is possibly causing confusion:

Here it excludes the slow clock only from VLPR mode [which is correct when the table handles only run mode and VLPR] but it states that the clock is disabled in VLLS mode and can continue running in STOP/VLPS when the correct registers bits are set.This now mixes the description with other low power modes and doesn't give information that it is only relevant for the fast IRC.

Only when understanding that this table is giving the rules for RUN and VLPR at the left and only giving partial details on the right - which then need to be "read together" with the low power mode rules of table 7-2 to get the overall rule set - does it all fall in to place.

Although it is not explicitly stated anywhere I uderstand that basically the slow IRC is stopped in ALL Vxxx modes so is only available in RUN, WAIT or STOP states.

Regards

Mark

Kinetis: µTasker Kinetis support

KL02: µTasker FRDM-KL02Z support

For the complete "out-of-the-box" Kinetis experience and faster time to market

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Martin

How are you determining whether the TPM is being clocked in VLPS?

According to the user's manual it continues as long as you have the IREFSTEN bit set before entering STOP or VLPS, but I can confirm that it doesn't allow PWM outputs to be used in VLPS (but they do operate in STOP mode, as long as the IREFSTEN bit is set). What I don't know at the moment is whether this is the TPM that doesn't operate or whether it is the PWM output (due to the port output not changing in the mode).

I have attached a binary that shows this on the FRDM-K02Z.

1. The TPM runs from the slow IRC and the IREFSTEN bit is set in MCG_C1. The output on PTB10 (blue LED) generates 20% PWM at 100Hz.

2. On the OpenSDA virtual COM there is a shell menu at 115'200 Baud. In the administrator menu low power modes can be set (eg. "set_lp 2" sets STOP mode and "set_lp 4" sets VLPS).

It is seen that the PWM output continues in STOP mode but stops (either at '1' or at '0') in VLPS mode.

3. The MCG_C1 register can be viewed in the I/O menu with the memory display command

"md 40064000 b 1"

and shows 0x03 (with IREFSTEN set).

The IREFSTEN can be disabled by commanding

"mm 40064000 b 2"

Repeating the low power mode tests as in 2 shows that now the PWM output stops in both STOP and VLPS modes.

Notes: After loading the binary to the board the board needs to be power cycled.

In both STOP and VLPS modes the UART will continue operating but will not be able to function correctly at 115200 Baud since the wakeup time is too slow. Therefore a reset is required to restart and do the next test.

Therefore with this binary I can confirm that PWM output stops in VLPS but continues in STOP as long as IREFSTEN is set (TPM clocked from slow IRC).

If this corresponds with your experience the question is whether the PWM output stops for a different reason, whereas the TPM is in fact still running (because slow IRC continues) or whether the TPM really completely stops in VLPS (due to the slow IRC being stopped), which would be contrary to the description in the user's manual?

Note finally that it operates as expected using the fast IRC as TPM clock.

Regards

Mark

Kinetis: µTasker Kinetis support

KL02: µTasker FRDM-KL02Z support

For the complete "out-of-the-box" Kinetis experience and faster time to market